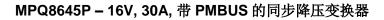

# **MPQ8645P** 16V, 30A, 带 PMBusTM 接口的

可扩展数字同步降压变换器

# 描述

MPQ8645P 是一款全集成、兼容 PMBus 接口的 高频同步降压变换器。MPQ8645P 提供了微小 体积的解决方案,在宽输入范围内每相可实现高 达 30A 的输出电流,具有极好的负载和线性调 节性能。MPQ8645P 在宽输出电流负载范围内 可高效工作。

PMBus 接口可以提供变换器配置和关键参数监 控功能。

MPQ8645P 采用 MPS 独有的多相恒定导通时间 控制模式 (MCOT),可提供快速瞬态响应和简单 的环路补偿。MCOT 控制方式还允许并联多个 MPQ8645P 设备,在用于大电流应用时可实现 极好的电流共享和相位交错功能。

全方位保护功能,包括过流保护(OCP)、过压 保护(OVP)、欠压保护(UVP)和过温保护 (OTP)。

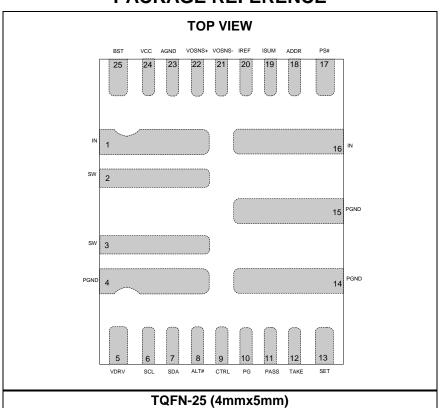

MPQ8645P 最大限度地减少了现有标准外部元器件的使用,采用 TQFN-25(4mmx5mm)封装。

# 特性

- 兼容 PMBus 1.3 标准

- 可扩展多相工作

- 3.1V 16V,外部 3.3V VCC 偏置

4V 16V,内部偏置或外部 3.3V VCC 偏置

- 每相连续输出电流为 30A

- 低导通阻抗集成功率 MOSFET

- 无损耗精确片上电流采样功能

- 用于超快瞬态响应的自适应恒定导通时间 (COT)控制

- 采用 Zero-ESR 输出电容可稳定工作

- 0°C 至 +70°C 结温范围内的参考电压精确度 为 0.5%

- 真实的输出电压远端采样功能

- 输出电压可调范围为 0.4V 至 0.9 x VIN,最 大可达 5.5V

- 输出电压/电流、输入电压和芯片内部温度报告

- 内置 MTP 存储个性化配置

- 可通过 PMBus 编程:

- o 输出电压

- o 输出电流限

- 跳频模式或强制连续导通工作模式 (FCCM)可选

- o 软启动时间

- 开关频率有 400kHz、600kHz、800kHz 或 1000kHz 4 种可选

- 。 用于 OCP, OVP 和 OTP 的自动恢复和 关断保护模式

- o 斜坡补偿

- 采用 TQFN-25 (4mmx5mm) 封装

## 应用

- 电信和网络系统

- 基站

- 服务器

所有 MPS 产品都保证无铅,无卤素,并且遵守 RoHS 规范。如需查询具体芯 片环保等级,请访问 MPS 官网之质量保证。"MPS"和"The Future of Analog IC Technology"均为 MPS 注册商标。

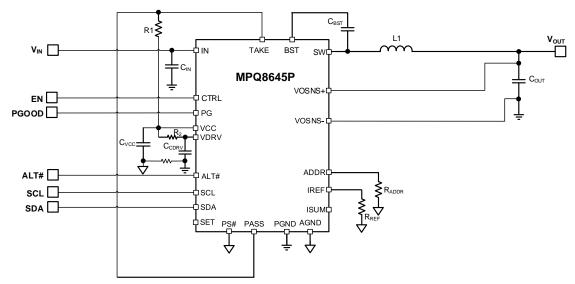

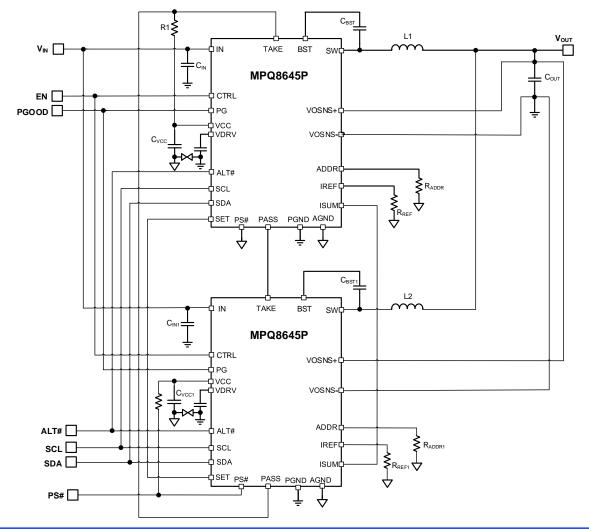

典型应用电路

单相工作

双相工作

## **ORDERING INFORMATION**

| Part Number*        | Package           | Top Marking |

|---------------------|-------------------|-------------|

| MPQ8645PGVT- xxxx** | TQFN-25 (4mmx5mm) | See Below   |

| EVKT-8645P          | Evaluation kit    | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MPQ8645PGVT-xxxx\*\*–Z).

\*\* "xxxx" is the configuration code identifier for the register settings stored in the MTP. The default number is "0000". Each "x" is a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number, even if ordering the "0000" code.

# **TOP MARKING**

MPSYWW M8645P LLLLLL

MPS: MPS prefix Y: Year code WW: Week code M8645P: Part number LLLLLL: Lot number

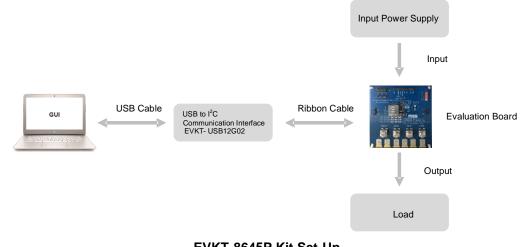

# **EVALUATION KIT EVKT-8645P**

EVKT-8645P contents: (Items below can be ordered separately).

| Item # | Part Number           | Item                                                                           | Quantity |

|--------|-----------------------|--------------------------------------------------------------------------------|----------|

| 1      | EVQ8645P-V-1Phase-00A | MPQ8645P single-phase evaluation board                                         | 1        |

| 2      | MPQ8645P software     | MPQ8645P GUI and driver for the USB<br>communication interface                 | 1        |

| 3      | EVKT-USBI2C-02        | One MPS PMBus USB communication interface, one USB cable, and one ribbon cable | 1        |

#### Order directly from monolithicpower.com or our distributors.

#### EVKT-8645P Kit Set-Up

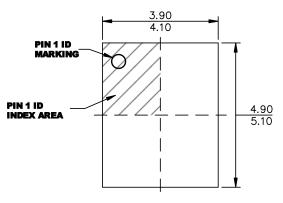

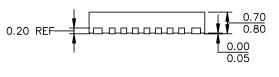

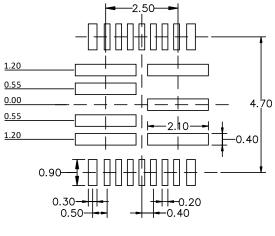

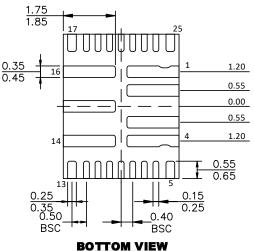

## **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| PIN #     | Name | Description                                                                                                                                                                                                                                                                                                                                                      |

|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 16     | IN   | <b>Supply voltage.</b> IN supplies power to the internal MOSFET and regulator. Use an input capacitor to decouple the input rail. Use wide PCB traces and multiple vias to make the connection.                                                                                                                                                                  |

| 2, 3      | SW   | <b>Switch output.</b> Connect SW to the inductor and bootstrap capacitor. SW is driven up to $V_{IN}$ by the high-side switch during the PWM duty cycle on time. The inductor current drives SW negative during the off time. Use wide PCB traces to make the connection.                                                                                        |

| 4, 14, 15 | PGND | <b>System ground.</b> PGND is the reference ground of the regulated output voltage, and requires careful consideration during PCB layout. Connect PGND with wide PCB traces.                                                                                                                                                                                     |

| 5         | VDRV | <b>Decoupling input pin for 3.3V driver power supply.</b> Decouple VDRV with a minimum $1\mu$ F ceramic capacitor placed as close to VDRV as possible. X7R or X5R grade dielectric ceramic capacitors are recommended. VDRV accepts an external 3.3V bias. If no external 3.3V bias is provided, connect VDRV to VCC through a $2\Omega$ to $10\Omega$ resistor. |

| 6         | SCL  | PMBus clock.                                                                                                                                                                                                                                                                                                                                                     |

| 7         | SDA  | PMBus data.                                                                                                                                                                                                                                                                                                                                                      |

| 8         | ALT# | <b>PMBus alert pin.</b> ALT# is active low. A pull-up resistor connected to 3.3V is required if the ALT# function is needed.                                                                                                                                                                                                                                     |

| 9         | CTRL | <b>PMBus control pin.</b> CTRL is a digital input that turns the regulator on or off with proper ON_OFF_CONFIG (02h) configuration. Drive CTRL high to turn on the regulator. Drive CTRL low to turn off the regulator. Do not float CTRL.                                                                                                                       |

| 10        | PG   | <b>Power good output.</b> The output of PG is an open-drain signal. PG requires a pull-up resistor connected to a DC voltage to indicate high if the output voltage exceeds 90% of the nominal voltage. There is a PGOOD delay from low to high. PG must be pulled high to ensure proper operation.                                                              |

# PIN FUNCTIONS (continued)

| PIN # | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11    | PASS   | Passes RUN signals to the next phase.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12    | TAKE   | <b>Receives RUN signals from the previous phase.</b> TAKE is used for master detection during the initial power-up. For the master phase, TAKE must be pulled high through a resistor. For the slave phase, TAKE is connected to the PASS of the previous phase.                                                                                                                                                                                   |

| 13    | SET    | <b>PWM signal.</b> SET turns the high-side MOSFET on when a RUN signal is present. For multi-phase operation, tie the SET pins of all phases together.                                                                                                                                                                                                                                                                                             |

| 17    | PS#    | <b>Phase shedding.</b> With proper PMBus setting, pull PS# high to enable a slave phase. Pull PS# low to disable a slave phase. Connect PS# of the master phase to AGND.                                                                                                                                                                                                                                                                           |

| 18    | ADDR   | <b>PMBus slave address-setting pin.</b> Connect a resistor from ADDR to AGND to set the address of this device.                                                                                                                                                                                                                                                                                                                                    |

| 19    | ISUM   | <b>Current-sense output.</b> For single-phase operation, keep ISUM floating. For multi-phase operation, tie the ISUM pins of all phases together for current sharing.                                                                                                                                                                                                                                                                              |

| 20    | IREF   | <b>Reference current generator amplifier output.</b> Connect a 60.4k $\Omega$ or 180k $\Omega$ resistor with 1% or higher accuracy to IREF.                                                                                                                                                                                                                                                                                                        |

| 21    | VOSNS- | <b>Output voltage sense negative return.</b> VOSNS- is tied directly to the GND sense point of the load. Connect VOSNS- to AGND if the remote sense is not used.                                                                                                                                                                                                                                                                                   |

| 22    | VOSNS+ | <b>Output voltage sense positive return.</b> Connect VOSNS+ to the output voltage sense positive side to provide feedback voltage to the system. Vias should be avoided on the VO traces.                                                                                                                                                                                                                                                          |

| 23    | AGND   | Analog ground. Select AGND as the control-circuit reference point.                                                                                                                                                                                                                                                                                                                                                                                 |

| 24    | VCC    | <b>Internal 3.3V LDO output.</b> VCC powers the analog and digital control circuits. Decouple VCC with a 1µF ceramic capacitor placed as close to VCC as possible. X7R or X5R grade dielectric ceramic capacitors are recommended. During MTP programming, a 5V voltage with a 300ms period may be observed on VCC. This VCC pin does not accept external voltage bias. For multi-phase applications, connect the VCC pins of all phases together. |

| 25    | BST    | <b>Bootstrap.</b> A capacitor connected between SW and BS is required to form a floating supply across the high-side switch driver.                                                                                                                                                                                                                                                                                                                |

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply voltage (V <sub>IN</sub> )                        | 18V      |

|----------------------------------------------------------|----------|

| V <sub>IN</sub> - V <sub>SW (DC)</sub> 0.3V t            | o 18.3V  |

| VIN - V <sub>SW (25nc)</sub> 5\                          | / to 25V |

| V <sub>SW (DC)</sub> 0.3V t                              | o 18.3V  |

| V <sub>SW (25ns)</sub> <sup>(2)</sup> 5\                 | / to 25V |

| V <sub>BST</sub>                                         | 22.3V    |

| V <sub>BST</sub> - V <sub>SW (25ns)</sub> <sup>(2)</sup> | 5V       |

| V <sub>CC</sub> , V <sub>DRV</sub>                       | 4.5V     |

| V <sub>CC (1s)</sub> <sup>(3)</sup>                      | 6V       |

| All other pins0.3V                                       | to 4.3V  |

| All other pins (1s) <sup>(3)</sup>                       |          |

| Junction temperature                                     | 170°C    |

| Lead temperature                                         |          |

| Storage temperature65°C to                               | +170°C   |

## **Recommended Operating Conditions** <sup>(4)</sup>

| Supply voltage (V <sub>IN</sub> )         | 4V to 16V      |

|-------------------------------------------|----------------|

| Output voltage (V <sub>OUT</sub> )        | 0.6V to 5.5V   |

| External V <sub>DRV</sub> bias            | 2.9V to 3.6V   |

| Operating junction temp (T <sub>J</sub> ) | 40°C to +125°C |

## Thermal Resistance<sup>(5)</sup> θ<sub>JB</sub> θ<sub>JC\_TOP</sub>

TQFN-25 (4mmx5mm) ......1.8......6.3... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) Specified by design. Measured by using a differential oscilloscope probe.

- 3) Voltage rating during MTP programming.

- 4) The device is not guaranteed to function outside of its operating conditions.

- 5)  $\dot{\theta}_{JB}$  is the thermal resistance from the junction to the board around the PGND soldering point.  $\theta_{JC_{TOP}}$  is the thermal resistance from the junction to the top of the package.

# **ELECTRICAL CHARACTERISTICS**

## $V_{IN}$ = 12V, $T_J$ = -40°C to +125°C, unless otherwise noted.

| Parameters                                                                         | Symbol                   | Condition                                                             | Min | Тур  | Max  | Units |

|------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------|-----|------|------|-------|

| V <sub>IN</sub> Supply Current                                                     | 1 -                      |                                                                       |     |      |      |       |

| Supply current (quiescent)                                                         | lin                      | V <sub>CTRL</sub> = 0V                                                |     | 2.5  | 4    | mA    |

| MOSFET                                                                             | I                        | •                                                                     |     |      |      |       |

| <u> </u>                                                                           | Ron <sub>Hs</sub>        | $T_J = 25^{\circ}C$                                                   |     | 4.4  |      |       |

| R <sub>DS(ON)</sub>                                                                | Ron <sub>LS</sub>        | $T_J = 25^{\circ}C$                                                   |     | 1.5  |      | mΩ    |

|                                                                                    | SWlkg_hs                 | SW = 0V                                                               |     | 0.1  | 10   |       |

| Switch leakage                                                                     | SW <sub>LKG_LS</sub>     | SW = 12V                                                              |     | 1    | 20   | μA    |

| Output Current Limit                                                               |                          |                                                                       | •   | •    | •    |       |

| Output current limit (inductor valley)                                             | I <sub>LIM_VALLEY</sub>  | D7h = 0x14                                                            | 27  | 30   | 33   | А     |

| Min output current limit<br>(inductor valley) programmable<br>value <sup>(6)</sup> | ILIM_VALLEY_MIN          |                                                                       |     | 1.5  |      | A     |

| Max output current limit<br>(inductor valley) programmable<br>value                | ILIM_VALLEY_MAX          |                                                                       | 36  | 40   | 44   | A     |

| Output current limit (DC)                                                          | ILIM_DC                  | 46h = 0x007C (per phase)                                              |     | 30   |      | А     |

| Min output over-current programmable value <sup>(6)</sup>                          | ILIM_DC_MIN              |                                                                       |     | 3    |      | А     |

| Max output over-current warning programmable value <sup>(6)</sup>                  | ILIM_DC_MAX              | 46h = 0x00BA (per phase)                                              |     | 45   |      | А     |

| Output over-current warning (DC)                                                   | Iwarn                    | 4Ah = 0x0074 (per phase)                                              | 25  | 28   | 31   | А     |

| Min output over-current warning programmable value <sup>(6)</sup>                  |                          |                                                                       |     | 3    |      | А     |

| Max output over-current warning programmable value <sup>(6)</sup>                  |                          | 4Ah = 0x00BA (per phase)                                              |     | 45   |      | А     |

| Low-side negative current limit                                                    |                          | D5h[2] = 1b'0                                                         |     | -13  |      | А     |

| in OVP                                                                             | LIM_NEG_OVP              | D5h[2] = 1b'1                                                         |     | -20  |      | А     |

| Low-side negative current limit in OSM <sup>(6)</sup>                              | I <sub>LIM_NEG_OSM</sub> |                                                                       |     | -10  |      | А     |

| Frequency and Timer                                                                |                          |                                                                       |     |      |      |       |

|                                                                                    |                          | $V_0 = 1V$ , $I_0 = 0A$ , $T_A = 25^{\circ}C$ ,<br>(D2h[2:1] = 2b'00) | 280 | 400  | 520  | kHz   |

| Switching froguency (6)                                                            | ferri                    | $V_0 = 1V, I_0 = 0A, T_A = 25^{\circ}C,$<br>(D2h[2:1] = 2b'01)        | 480 | 600  | 720  | kHz   |

| Switching frequency <sup>(6)</sup>                                                 | fsw                      | $V_0 = 1V$ , $I_0 = 0A$ , $T_A = 25^{\circ}C$ ,<br>(D2h[2:1] = 2b'10) | 680 | 800  | 920  | kHz   |

|                                                                                    |                          | $V_0 = 1V, I_0 = 0A, T_A = 25^{\circ}C,$<br>(D2h[2:1] = 2b'11)        | 850 | 1000 | 1150 | kHz   |

| Minimum on time (6)                                                                | ton_min                  | $f_{SW} = 1000 kHz, V_0 = 0.6V$                                       |     |      | 50   | ns    |

| Minimum off time (6)                                                               | toff_min                 | V <sub>FB</sub> = 580mV                                               |     |      | 220  | ns    |

## $V_{IN} = 12V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , unless otherwise noted.

| Parameters                       | Symbol                         | Condition                               | Min  | Тур    | Мах  | Units      |

|----------------------------------|--------------------------------|-----------------------------------------|------|--------|------|------------|

| Output Over-Voltage and Under    | er-Voltage Pro                 | otection (OVP, UVP)                     |      |        |      |            |

| OVP threshold                    | V <sub>OVP</sub>               | Default setting (D4h[1:0] = 2b'00)      | 112% | 115%   |      | $V_{REF}$  |

| UVP threshold                    | Vuvp                           | Default setting (D9h[3:2] = 2b'10)      | 76%  | 79%    | 83%  | Vref       |

| Max programmable OVP threshold   | Vovp_max                       | D4h[1:0] = 2b'11                        | 127% | 130%   | 133% | Vref       |

| Min programmable OVP threshold   | Vovp_min                       | D4h[1:0] = 2b'00                        | 112% | 115%   |      | Vref       |

| OVP threshold resolution         |                                | Per LSB                                 |      | 5%     |      | $V_{REF}$  |

| Max programmable UVP threshold   | V <sub>UVP_max</sub>           | D9h[3:2] = 2b'11                        | 81%  | 84%    | 88%  | $V_{REF}$  |

| Min programmable UVP threshold   | Vuvp_min                       | D9h[3:2] = 2b'00                        | 66%  | 69%    | 72%  | Vref       |

| UVP threshold resolution         |                                | Per LSB                                 |      | 5%     |      | $V_{REF}$  |

| OSM threshold rising             | V <sub>OSM_RISE</sub>          | EAh[9] = 1b'0                           |      | 104.8% |      | $V_{REF}$  |

| OSM threshold falling            | $V_{\text{OSM}_{\text{FALL}}}$ |                                         |      | 102.2% |      | $V_{REF}$  |

| CTRL                             |                                |                                         | -    |        |      |            |

| Input high voltage               | VIH_CTRL                       |                                         | 2.15 |        |      | V          |

| Input low voltage                | VIL_CTRL                       |                                         |      |        | 1.20 | V          |

| ADC <sup>(6)</sup>               |                                |                                         | •    |        |      |            |

| Input voltage range              |                                |                                         | 0    |        | 1.28 | V          |

| ADC resolution                   |                                |                                         |      | 10     |      | Bits       |

| DNL                              |                                |                                         |      | 1      |      | LSB        |

| Sample rate                      |                                |                                         |      | 3      |      | kHz        |

| DAC (Feedback Voltage)           |                                |                                         |      | I      |      |            |

| Range                            |                                |                                         | 512  | 600    | 672  | mV         |

| Feedback accuracy                | Vfb                            | 21h = 0x012C, D1h[1:0] = 2b'00          | 594  | 600    | 606  | mV         |

| Resolution                       |                                | Per LSB                                 |      | 2      |      | mV         |

| Output voltage slew rate         |                                | Default setting (DAh[3:0] =<br>4b'0000) |      | 20     |      | μs/<br>2mV |

| Minimum output voltage slew rate |                                | DAh[3:0] = 4b'1111                      | 30   | 40     | 50   | μs/<br>2mV |

| Maximum output voltage slew rate |                                | DAh[3:0] = 4b'0000                      |      | 20     |      | μs/<br>2mV |

## $V_{IN}$ = 12V, $T_J$ = -40°C to +125°C, unless otherwise noted.

| Parameters                                                 | Symbol                                  | Condition             | Min  | Тур   | Max  | Units |

|------------------------------------------------------------|-----------------------------------------|-----------------------|------|-------|------|-------|

| Maximum feedback voltage with margin <sup>(6)</sup>        | Vfb_mg_high_<br>max                     |                       |      | 672   |      | mV    |

| Minimum feedback voltage with margin <sup>(6)</sup>        | V <sub>FB_MG_LOW_</sub><br>MIN          |                       |      | 512   |      | mV    |

| Feedback voltage with margin high <sup>(6)</sup>           | Vfb_mg_high                             |                       |      | 672   |      | mV    |

| Feedback voltage with margin low <sup>(6)</sup>            | Vfb_mg_low                              |                       |      | 512   |      | mV    |

| Soft Start and Turn-On Delay                               |                                         |                       |      |       |      |       |

| Soft-start time                                            | tss                                     | 61h[2:0] = 3b'001     | 1.7  | 2.3   | 3.0  | ms    |

| Min programmable soft-start time <sup>(6)</sup>            | tss_min                                 | 61h[2:0] = 3b'000     |      | 1     |      | ms    |

| Max programmable soft-start time <sup>(6)</sup>            | tss_max                                 |                       |      | 16    |      | ms    |

| Turn-on delay                                              | ton_delay                               | 60h = 0x0001          | 3.9  | 4.5   | 5.1  | ms    |

| Min turn-on delay <sup>(6)</sup>                           | ton_delay_Min                           | 60h = 0x0000          |      | 0     |      | ms    |

| Max turn-on delay (6)                                      | t <sub>ON_DELAY_Max</sub>               | 60h = 0x0100          |      | 1024  |      | ms    |

| Error Amplifier                                            |                                         |                       |      |       |      |       |

| Feedback current                                           | I <sub>FB</sub>                         | Vfb = Vref            |      | 50    | 100  | nA    |

| Soft Shutdown                                              |                                         |                       |      |       |      |       |

| Soft shutdown discharge<br>MOSFET                          | Ron_disch                               | T <sub>J</sub> = 25°C |      | 60    | 120  | Ω     |

| Under-Voltage Lockout (UVLC                                | D)                                      |                       |      |       |      |       |

| VCC under-voltage lockout threshold rising                 | VCCvth_Rise                             |                       | 2.60 | 2.75  | 2.9  | V     |

| VCC under-voltage lockout threshold falling                | VCC <sub>Vth_Fall</sub>                 |                       | 2.35 | 2.50  | 2.65 | V     |

| VCC output voltage                                         | Vcc                                     |                       | 3.10 | 3.25  | 3.40 | V     |

| Min input programmable turn-<br>on voltage                 | Vin_on_min                              | VCC = 3.3V            | 2.65 | 2.90  | 3.1  | V     |

| Max input programmable turn-<br>on voltage                 | Vin_on_max                              |                       | 16   | 16.5  | 17   | V     |

| Min input programmable turn-<br>off voltage <sup>(6)</sup> | $V_{\text{IN}\_\text{OFF}\_\text{MIN}}$ | VCC = 3.3V            | 2.5  | 2.75  | 3    | V     |

| Max input programmable turn-<br>off voltage                | Vin_off_max                             |                       |      | 15.75 |      | V     |

| VDRV under-voltage lockout threshold rising                | VDRV <sub>Vth_Rise</sub>                |                       | 2.55 | 2.75  | 2.95 | V     |

| VDRV under-voltage lockout threshold falling               | VDRV <sub>Vth_Fall</sub>                |                       | 2.15 | 2.35  | 2.55 | V     |

## $V_{IN} = 12V$ , $T_J = -40^{\circ}C$ to $+125^{\circ}C$ , unless otherwise noted.

| Parameters                                      | Symbol                    | Condition                                                                                        | Min  | Тур  | Max  | Units            |  |

|-------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------|------|------|------|------------------|--|

| Power Good (PG)                                 |                           |                                                                                                  |      |      |      |                  |  |

| Power good high threshold                       | PG <sub>Vth_Hi_Rise</sub> | FB from low to high, default setting (D9h[1:0] = 2b'01)                                          | 91%  | 94%  | 97%  | Vref             |  |

| Power good low threshold                        | PG <sub>Vth_Lo_Rise</sub> | FB from low to high, default<br>setting (D4h[1:0] = 2b'00)                                       | 112% | 115% | 118% | V <sub>REF</sub> |  |

| Power good low intestiond                       | PG <sub>Vth_Lo_Fall</sub> | FB from high to low, default setting (D9h[3:2] = 2'b10)                                          | 76%  | 79%  | 83%  | Vref             |  |

| Power good low-to-high delay                    | PG <sub>Td</sub>          | Default setting (D1h[5:2] =<br>4b'0000)                                                          | 1.6  | 2.0  | 2.4  | ms               |  |

| Power good sink current<br>capability           | Vpg                       | I <sub>PG</sub> = 10mA                                                                           |      |      | 0.3  | V                |  |

| Power good leakage current                      | IPG_LEAK                  | V <sub>PG</sub> = 3V                                                                             |      | 1.5  | 2.3  | μA               |  |

| Power good low-level output                     | Vol_100                   | $V_{IN} = 0V$ , pull PGOOD up to 3.3V through a 100k $\Omega$ resistor,<br>T <sub>J</sub> = 25°C |      | 600  | 720  |                  |  |

| voltage                                         | Vol_10                    | $V_{IN} = 0V$ , pull PGOOD up to 3.3V through a $10k\Omega$ resistor,<br>T <sub>J</sub> = 25°C   |      | 700  | 820  | mV<br>0          |  |

| Thermal Protection (TP)                         |                           |                                                                                                  |      |      |      |                  |  |

| TP fault rising threshold (6)                   | T <sub>SD_Rise</sub>      | Default setting (4Fh = 0x0091)                                                                   |      | 145  |      | °C               |  |

| TP fault falling threshold <sup>(6)</sup>       | T <sub>SD_Fall</sub>      | Default setting (4Fh = 0x007D<br>and D6h[2:1] = 2b'00)                                           |      | 125  |      | °C               |  |

| Min TP fault temp (6)                           | T <sub>SD_WARN_MIN</sub>  |                                                                                                  |      | 35   |      | °C               |  |

| Max TP fault temp (6)                           | T <sub>SD_WARN_MAX</sub>  |                                                                                                  |      | 165  |      | °C               |  |

| TP warning rising threshold <sup>(6)</sup>      | Twarn_Rise                | Default setting (4Ah = 0x0078)                                                                   |      | 120  |      | °C               |  |

| TP warning falling threshold (6)                | Twarn_Fall                | Default setting (4Ah = 0x0078,<br>D6h[2:1] = 2b'00)                                              |      | 100  |      | °C               |  |

| Min TP warning temp <sup>(6)</sup>              | TSD_WARN_MIN              |                                                                                                  |      | 35   |      | °C               |  |

| Max TP warning temp (6)                         | TSD_WARN_MAX              |                                                                                                  |      | 160  |      | °C               |  |

| Monitoring Parameters                           |                           |                                                                                                  |      |      |      |                  |  |

| Min output voltage monitor range <sup>(6)</sup> | Mvout_range               |                                                                                                  |      | 0    |      | V                |  |

| Max output voltage monitor range <sup>(6)</sup> | Mvout_range               |                                                                                                  |      | 5.5  |      | V                |  |

| Output voltage monitor accuracy <sup>(6)</sup>  | M <sub>VOUT_ACC</sub>     | $V_0 = 0.6V$ to 2.5V                                                                             | -2%  | 0.6  | 2%   | V                |  |

| Output voltage monitor accuracy <sup>(6)</sup>  | Mvout_acc                 | $V_0 = 2.5V$ to 5.5V                                                                             | 50   |      | 50   | mV               |  |

| Output voltage bit resolution                   |                           |                                                                                                  |      | 1.25 |      | mV               |  |

| Output current monitor accuracy                 | MIOUT_ACC                 | $V_0 = 1.2V$ , f <sub>SW</sub> = 800kHz,<br>$I_0 = 30A$                                          | -2.5 |      | 2.5  | А                |  |

| Output current monitor accuracy <sup>(6)</sup>  | MIOUT_ACC                 | 3A ≤ I <sub>0</sub> ≤30A                                                                         | -2.5 |      | 2.5  | А                |  |

## $V_{IN}$ = 12V, $T_J$ = -40°C to +125°C, unless otherwise noted.

| Parameters                                   | Symbol           | Condition                           | Min  | Тур  | Max  | Units |

|----------------------------------------------|------------------|-------------------------------------|------|------|------|-------|

| Output current bit resolution <sup>(6)</sup> |                  |                                     |      | 62.5 |      | mA    |

| Min input voltage monitor <sup>(6)</sup>     | Min_range        |                                     |      | 2.5  |      | V     |

| Max input voltage monitor <sup>(6)</sup>     | Min_range        |                                     |      | 18   |      | V     |

| Input voltage monitor accuracy               | MIN_ACC          |                                     | -2%  | 12   | 2%   | V     |

| Input voltage bit resolution (7)             |                  |                                     |      | 25   |      | mV    |

| PMBus DC Characteristics (SI                 | DA, SCL, ALT     | <b>#, CTRL)</b> <sup>(6)</sup>      |      |      |      |       |

| Input high voltage                           | VIH              |                                     |      |      | 2.1  | V     |

| Input low voltage                            | VIL              |                                     | 0.8  |      |      | V     |

| Output low voltage                           | Vol              | lo∟ = 1mA                           |      |      | 0.4  | V     |

| Input leakage current                        | ILEAK            | SDA, SCL, ALT# = 3.3V               | -10  |      | 10   | μA    |

| Maximum voltage (SDA, SCL,<br>ALT#, CTRL)    | VMAX             | Transient voltage including ringing | -0.3 | 3.3  | 3.6  | V     |

| Pin capacitance on SDA,SCL                   | CPIN             |                                     |      |      | 10   | pF    |

| PMBus Timing Characteristics                 | S <sup>(7)</sup> |                                     |      |      |      |       |

| Min operating frequency                      |                  |                                     |      | 10   |      | kHz   |

| Max operating frequency                      |                  |                                     |      | 1000 |      | kHz   |

| Bus free time                                |                  | Between stop and start condition    | 4.7  |      |      | μs    |

| Holding time                                 |                  |                                     | 4.0  |      |      | μs    |

| Repeated start condition set-<br>up time     |                  |                                     | 4.7  |      |      | μs    |

| Stop condition set-up time                   |                  |                                     | 4.0  |      |      | μs    |

| Data hold time                               |                  |                                     | 300  |      |      | ns    |

| Data set-up time                             |                  |                                     | 250  |      |      | ns    |

| Clock low time-out                           |                  |                                     | 25   |      | 35   | ms    |

| Clock low period                             |                  |                                     | 4.7  |      |      | μs    |

| Clock high period                            |                  |                                     | 4.0  |      | 50   | μs    |

| Clock/data fall time                         |                  |                                     |      |      | 300  | ns    |

| Clock/data rise time                         |                  |                                     |      |      | 1000 | ns    |

Notes:

6) Guaranteed by design.

7) Guaranteed by design, not tested in production. The parameter is tested during parameter characterization.

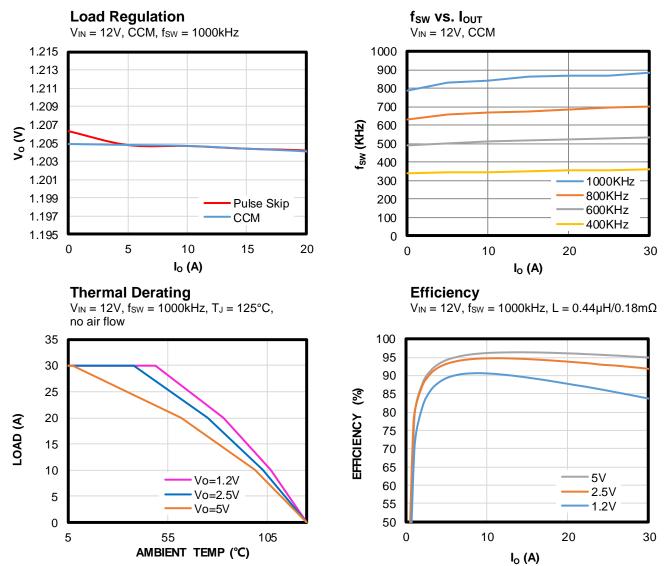

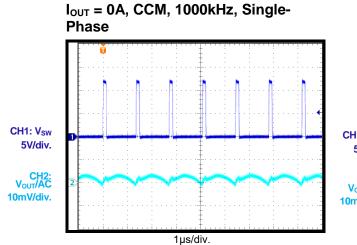

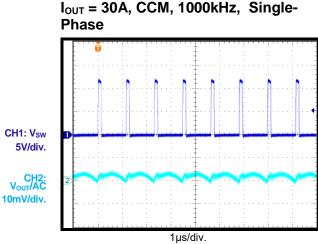

# **TYPICAL PERFORMANCE CHARACTERISTICS**

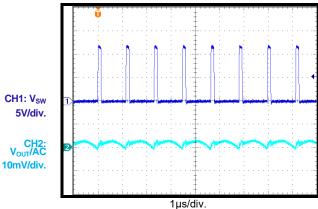

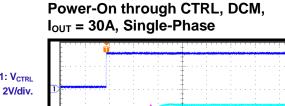

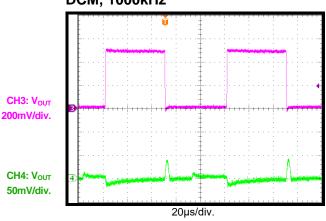

IOUT = 0A, DCM, 1000kHz, Single-

Phase

CH1: V<sub>sw</sub> 5V/div.

CH2: V<sub>OUT</sub>/AC 10mV/div.

4ms/div.

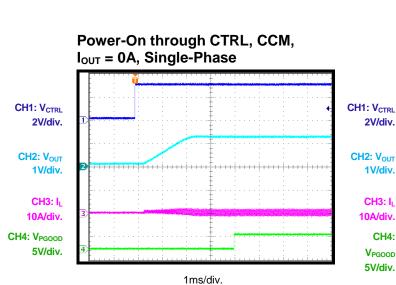

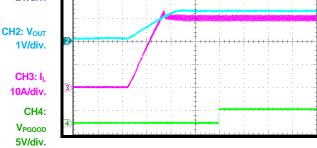

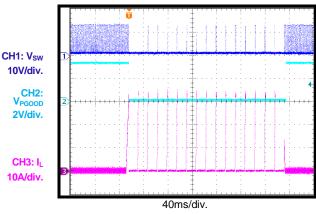

# Power-On through CTRL, CCM, $I_{OUT} = 30A$ , Single-Phase

1ms/div.

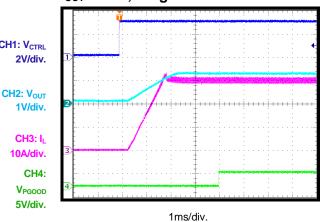

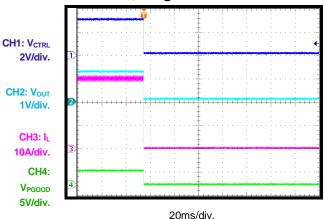

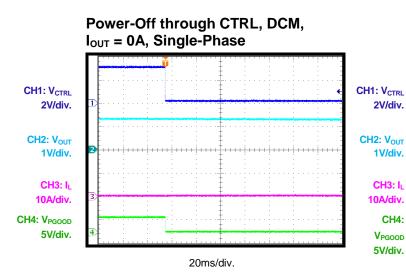

Power-Off through CTRL, CCM, I<sub>OUT</sub> = 0A, Single-Phase

Power-Off through CTRL, CCM, I<sub>OUT</sub> = 30A, Single-Phase

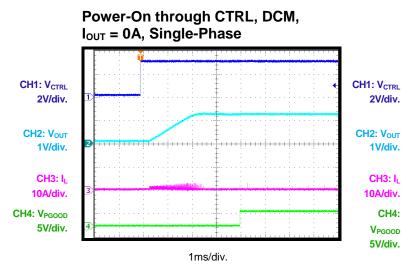

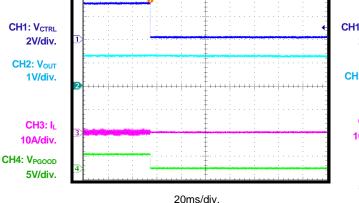

## Power-Off through CTRL, DCM, I<sub>OUT</sub> = 30A, Single-Phase

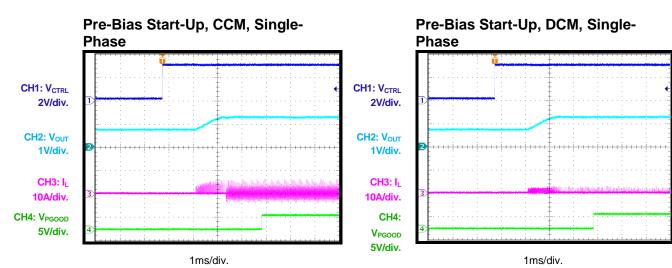

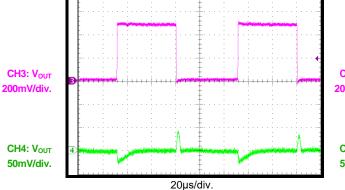

Load Transient, I<sub>OUT</sub> = 0A to 10A, CCM, 1000kHz

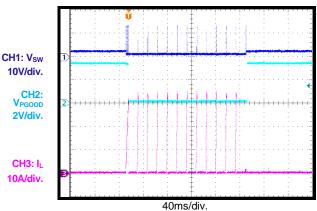

CH1: V<sub>SW</sub> 10V/div. CH2: V<sub>PGOOD</sub> 2V/div. CH3: I<sub>L</sub> 10A/div. Load Transient, I<sub>OUT</sub> = 0A to 10A, DCM, 1000kHz

# OCP, Hiccup Option, CCM, Single-Phase

OCP, Hiccup Option, DCM, Single-Phase

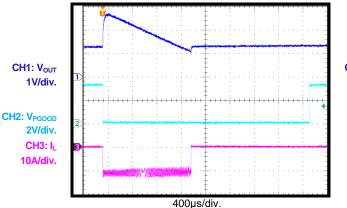

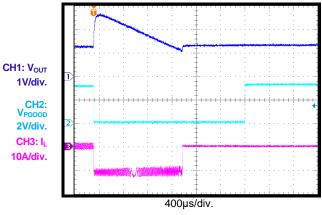

### OVP, Hiccup Option, CCM, Single-Phase

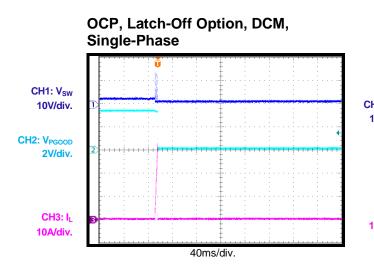

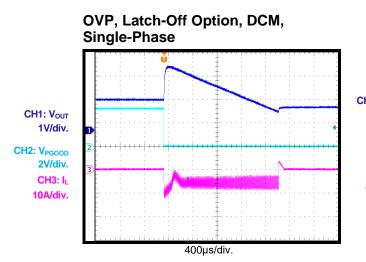

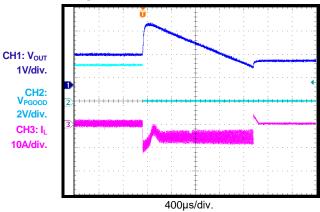

# OVP, Latch-Off Option, CCM, Single-Phase

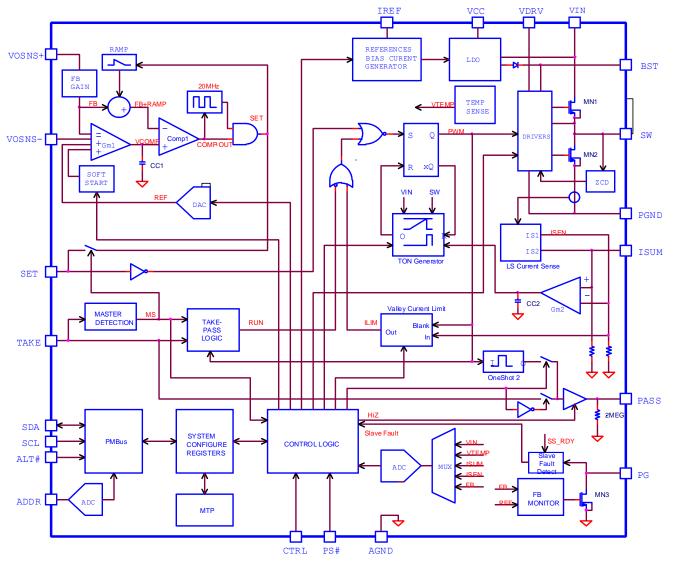

# FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

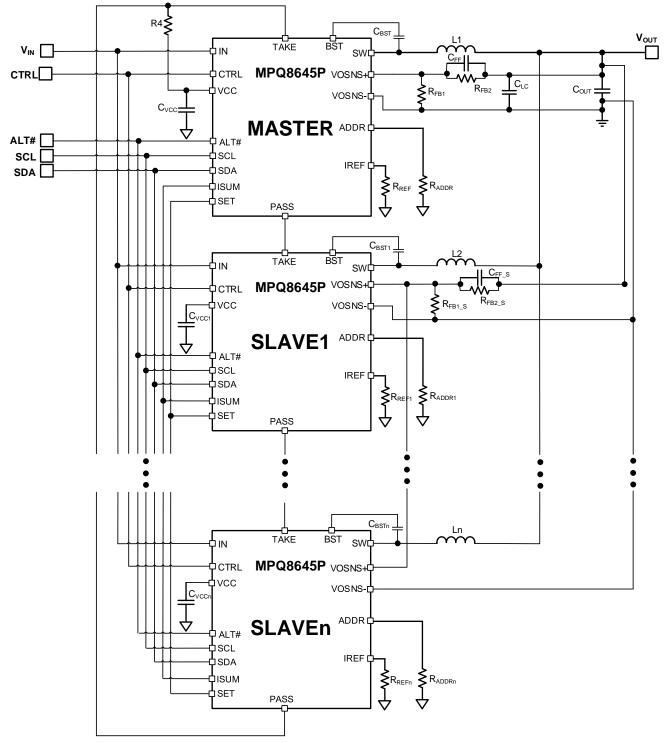

# **MULTI-PHASE OPERATION**

Figure 2: Multi-Phase (n+1) Configuration

## **MULTI-PHASE OPERATION** (continued)

Figure 4: Multi-Phase Interleaved Operation (Load Step-Up Response)

# OPERATION

## MCOT OPERATION

The MPQ8645P fully is а integrated. switch-mode synchronous, step-down, converter that uses multi-phase constant-ontime (COT) control to provide a fast transient The selectable internal response. ramp compensation stabilizes the system and makes it easy to use.

### Master/Slave Auto-Detection

One master phase is needed for both singleand multiple-phase operation. To be configured as a master phase, the TAKE pin of the phase must be pulled high to a voltage source. The PASS/TAKE pins of all phases are connected in a daisy chain configuration. The PASS pin of the last phase is connected back to the TAKE pin of the first (master) phase. For single-phase operation, the PASS and TAKE pins are connected together. After power-up, the master phase is determined, and the rest of phases are slave phases.

## MCOT Operation (Master)

The master phase has the following functions:

- Accepts both write and read commands through the PMBus from the system.

- Generates the SET signals.

- Manages start-up, shutdown, and all protections.

- Monitors fault alerts from the slave phases through the PG pin.

- Starts the first on pulse.

- Starts the on pulse when receiving RUN and SET signals.

- Determines the on pulse width of its own phase based on the per-phase and total current.

- Carries on the PASS/TAKE signal.

## MCOT Operation (Slave)

The slave phase has the following functions:

- Accepts write commands through the PMBus from the system.

- Takes the SET signal from the master.

- Sends an OV/UV/OT alert to the master through PG.

- Starts the on pulse when receiving RUN and SET signals.

- Determines the on pulse width of its own phase based on the per-phase and total current.

- Carries on the PASS/TAKE signal.

Figure 3 shows the details of MCOT operation.

At t0, VFB + RAMP drops below the reference level (VCOMP) in the master phase and generates a SET signal. All phases receive this SET signal, but only the phase that has the active RUN signal takes action (the master, in this case). Therefore, the master turns on the high-side MOSFET (HS-FET). Meanwhile, a fixed on pulse is generated on PASS, and this signal is passed to the TAKE pin of Slave 1.

At t1, the falling edge of the TAKE pin of Slave 1 activates the RUN signal. From this point on, Slave 1 is waiting for the SET signal to turn on the HS-FET.

At t2, the on pulse of the master phase expires, and the HS-FET turns off. The on-pulse width is fixed with the given input voltage, output voltage, and selected switching frequency. The on pulse width is fine-tuned based on the perphase and total currents.

At t3, VFB + RAMP drops below VCOMP in the master phase again. Only Slave 1 has an active RUN signal, so it turns on its HS-FET. All other phases ignore this SET signal. Meanwhile, Slave 1 generates a fixed on pulse on PASS, and this on pulse is passed to the TAKE pin of Slave 2.

The above operation continues, and the phase turns on its HS-FETs one by one for a fixed on time. The operation is carried on through the PASS/TAKE loop, and only the phase that has the RUN signal turns on the HS-FET when the SET signal is ready.

The MPQ8645P utilizes constant-on-time (COT) control, which provides super-fast load transient response. When a load step-up occurs, the FB signal is lower than REF, so the SET signal is generated more frequently than during steady state to respond to the load

transient. This depends on the load transient step size and slew rate. The SET signal can be

generated with the minimum 50ns interval (i.e. the next phase can be turned on in as little as 50ns after the turn-on of the previous phase to provide super-fast load transient response). Figure 4 shows the detailed operation.

#### **Ramp Compensation**

MPQ8645P provides The internal ramp compensation to support all types of output capacitors. Only the master phase utilizes ramp compensation. Whenever a SET signal is generated, the ramp is increased with a certain amount of amplitude in a fixed period. The ramp is then discharged with an adaptive slew rate. This ramp signal is superimposed to the FB signal, so when the superimposed ramp + FB signal reaches the REF signal, a new SET signal is generated. The ramp is selectable through the PMBus command of D0h[3:1] to support а wide range of operation configurations. The larger the ramp is, the less jitter the system will have. However, a larger ramp also results in slower load transient response. It is recommended to choose an optimal ramp based on your particular design if load transient response is a critical design target.

In single-phase operation, the ramp does not need to be reset by the SET signal, and can be reset by pulse-width modulation (PWM) instead. This option can be selected through the PMBus command EAh[3]. When EAh[3] = 0, the ramp is reset by PWM. This is only for single-phase operation. When EAh[3] = 1b'1, the ramp is reset by the SET signal. This is optimal for both single-phase and multi-phase operations.

#### **Mode Selection**

The MPQ8645P provides both forced continuous conduction mode (CCM) operation and pulse-skip operation under light-load condition. The operation mode can be chosen through the PMBus command D2h[0]. When D2h[0] = 1b'1, the device operates in CCM. When D2h[0] = 0, the device operates in pulse-skip operation.

## Phase-Shedding Operation (Slave)

For multi-phase operation, slave phases can be enabled or disabled through the PMBus or PS# pin. The phase-shedding function is disabled in the master phase to ensure proper operation. If phase shedding is controlled through the PMBus, the E5h[0] command is used. When E5h[0] = 1b'0, slave phases are enabled. When E5h[0] = 1b'1, slave phases are disabled.

If phase shedding is controlled through the PS# pin, the E5h[1] command must be set to 1b'1. In this way, the slave phases are enabled when PS# is pulled high. Slave phases are disabled when PS# is pulled low.

### Soft Start (SS)

The soft-start (SS) time can be programmed through the PMBus command TON\_RISE (61h). The minimum SS time is 1ms when 61h = 0x0000. Selectable SS time options include 1ms, 2ms, 4ms, 8ms, and 16ms.

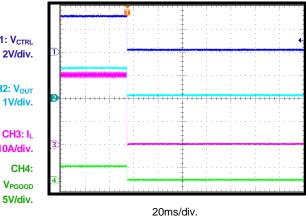

### Pre-Bias Start-Up

The MPQ8645P is designed for monotonic start-up into pre-biased loads. If the output voltage is pre-biased to a certain voltage during start-up, the IC disables switching for both the high-side and low-side switches until the internal reference voltage exceeds the sensed output voltage at the FB pin. Before the reference voltage reaches the pre-biased FB level, if the BST voltage is lower than the 2.4V threshold, the low-side MOSFET (LS-FET) is forced on for about 200ns to charge up the BST voltage.

## **Output Voltage Discharge**

When the MPQ8645P is disabled through CTRL or the PMBus OPERATION command, output voltage discharge mode is enabled if this function is selected. Both the HS-FET and the LS-FET are latched off. A discharge MOSFET connected between SW and GND turns on to discharge the output voltage. The typical switch on resistance of this MOSFET is about 50 $\Omega$ . Once the FB voltage drops below 10% \* REF, the discharge MOSFET turns off. This feature can be enabled or disabled through PMBus command MFR\_CTRL\_01 (D1h[6]).

# Current Sense and Over-Current Protection (OCP)

The MPQ8645P features on-die current sensing and a programmable, positive, current-limit threshold. The MPQ8645P provides both inductor valley current limiting (set by the PMBus command D7h) and output DC limiting

(set by the PMBus command 46h).

# Inductor Valley Over-Current Protection (D7h)

During the LS-FET on state, the SW current (inductor current) is sensed and monitored cycle by cycle. When FB drops below the reference, the HS-FET is only allowed to turn on whenever no over-current (OC) condition is detected during the LS-FET on state. Therefore, the inductor current is limited cycle by cycle. If 31 consecutive cycles of an OC condition are detected, over-current protection (OCP) is triggered.

During an OC or output short-circuit condition, if the output voltage drops below the undervoltage protection (UVP) threshold, the device enters OCP immediately.

Once OCP is triggered, the device either enters hiccup mode or latches off, depending on the PMBus selection. If it latches off, VCC or VIN must be power recycled to enable the part again.

The inductor valley over-current limit can be programmed through the PMBus command D7h. D7h only sets the per-phase inductor valley current limit, regardless of whether the device is operating in single-phase or multiphase operation.

## Output Over-Current (DC) Protection (46h)

The output DC current is sensed and monitored during operation. During an OC condition, if the sensed output DC current exceeds the 46h setting, the device enters OCP immediately.

Once OCP is triggered, the device enters hiccup mode or latches off, depending on the PMBus selection. If it latches off, VCC or VIN must be power recycled to enable the part again. The output over-current DC limit can be programmed through the PMBus command 46h, which limits the total output current of the rail.

## Negative Inductor Current Limit

When the LS-FET detects a negative current lower than the limit set through the PMBus D5h[2] command, the part turns off the LS-FET for a certain period of time to limit the negative current. This period is set through the PMBus command D5h[3].

## Under-Voltage Protection (UVP)

The MPQ8645P monitors the output voltage using the FB pin connected to the tap of a resistor divider to detect an under-voltage condition. If the FB voltage drops below the under-voltage protection (UVP) threshold (set through the PMBus VOUT\_UV\_FAULT\_ LIMIT command), UVP is triggered. After UVP is triggered, the device either enters hiccup mode or latches off, depending on the PMBus selection. If it latches off, VCC or CTRL must be power recycled to enable the part again.

## **Over-Voltage Protection (OVP)**

The MPQ8645P monitors the output voltage using the FB pin connected to the tap of a resistor divider to detect an over-voltage condition. See the MFR\_OVP\_NOCP\_SET section on page 46 for detailed OVP responses.

## Output Sinking Mode (OSM)

The MPQ8645P employs an output-sinking mode (OSM) to regulate the output voltage to the targeted value. When the FB voltage is above 105% \* REF but below the OVP threshold, OSM is triggered. During OSM, the MPQ8645P runs in forced CCM. The device exits OSM when the HS-FET turns back on. OSM can be enabled and disabled through the PMBus command EAh bit[9].

## Over-Temperature Protection (OTP)

The MPQ8645P has over-temperature protection (OTP). The IC monitors the junction temperature internally. lf the junction temperature exceeds the threshold value (set through the **PMBus** command OT\_FAULT\_LIMIT), the converter shuts off. After OTP is triggered, the device either enters hiccup mode or latches off, depending on the PMBus command MFR\_OVP\_NOCP\_SET. If it latches off, VCC or CTRL must be power recycled to enable the part again.

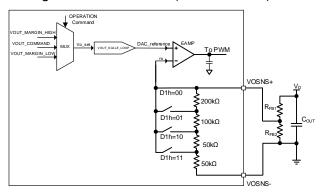

## Output Voltage Setting

The internal DAC reference range of the MPQ8645P is 162mV to 672mV. To achieve a higher output voltage, an external or internal voltage divider can be selected. VOUT SCALE LOOP (29h) and (D1h[1:0]) MFR CTRL VOUT are used together to set different output voltages. Table 1

shows the relationship of VOUT\_SCALE\_LOOP (29h) and MFR\_CTRL\_VOUT (D1h[1:0]).

Table 1: VOUT\_SCALE\_LOOP vs MFR\_CTRL\_VOUT

| FB<br>Divider | VOUT_SCALE_<br>LOOP (29h)                                          | MFR_CTRL_VOUT<br>(D1h[1:0]) |

|---------------|--------------------------------------------------------------------|-----------------------------|

| External      | 29h = R <sub>FB2</sub> /<br>(R <sub>FB1</sub> + R <sub>FB2</sub> ) | D1h[1:0] = 2'b00            |

|               | 29h = 0x03E8                                                       | D1h[1:0] = 2'b00            |

| Internal      | 29h = 0x01F4                                                       | D1h[1:0] = 2'b01            |

| memai         | 29h = 0x00FA                                                       | D1h[1:0] = 2'b10            |

|               | 29h = 0x007D                                                       | D1h[1:0] = 2'b11            |

It is *not* recommended to change VOUT\_SCALE\_LOOP (29h) and MFR\_CTRL\_VOUT (D1h[1:0]) when the power stage is enabled.

## **External Voltage Divider**

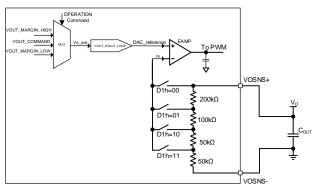

If an external voltage divider is used to set the output voltage, the MFR\_CTRL\_VOUT (D1h) can only be set to D1[0:0] = 2'b00. Figure 5 shows the configuration of an external voltage divider used. VOSNS+ and VOSNS- are connected to the output voltage sense point through a resistor divider ( $R_{FB1}$  and  $R_{FB2}$ ).

#### Figure 5: Output Voltage Set by External Resistor Divider

The MPQ8645P provides output voltage monitoring through register READ\_VOUT (8Bh). To achieve the correct output voltage setting and monitoring, the registers VOUT\_COMMAND (21h), VOUT\_MARGIN\_ HIGH (25h), VOUT\_MARGIN\_LOW (26h), and VOUT\_SCALE\_LOOP (29h) should be set correspondingly. The steps below show how to set the output voltage to 2.5V:

- 1. Determine the Vo\_set source based on the OPERATION (01h) command. Assume that VOUT\_COMMAND (21h) is selected.

- 2. Set D1[1:0] to 2'b00 for the external voltage divider option.

- 3. Select  $R_{FB1}$  and  $R_{FB2}$  to have a 600mV FB voltage. In this case,  $R_{FB2}$  / ( $R_{FB1}$  +  $R_{FB2}$ ) = 0.24.

- 4. Set the VOUT\_SCALE\_LOOP (29h) to 0x00F0 to match the external voltage divider ratio (0.24).

- 5. Set the VOUT\_COMMAND (21h) to 0x04E2 (LSB = 2mV). VOUT\_COMMAND = 600mV / VOUT\_SCALE\_LOOP.

- 6. VOUT\_COMMAND (21h) must be sent after VOUT\_SCALE\_LOOP (29h) and D1h. Otherwise, the change of VOUT\_SCALE\_ LOOP (29h) and D1h will not be effective.

### Internal Voltage Divider

Figure 6 shows the configuration of the internal voltage divider. VOSNS+ and VOSNS- are connected directly to the output voltage sense point.

#### Figure 6: Output Voltage Set by Internal Resistors Divider

Table 2 shows the internal voltage divider options through MFR\_CTRL\_VOUT (D1h).

# Table 2: Output Voltage Range with Internal Voltage Divider

| MFR_CTRL_VOUT (D1h) |                                                                               |  |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------|--|--|--|--|--|

| Bits                | Description                                                                   |  |  |  |  |  |

|                     | 2'b00: $V_{\text{REF}}$ / $V_{\text{O}}$ = 1, $V_{\text{O}}$ = 0.4V to 0.672V |  |  |  |  |  |

| [1:0]               | 2'b01: $V_{REF} / V_0 = 0.5$ , $V_0 = 0.4V$ to 1.344V                         |  |  |  |  |  |

|                     | 2'b10: $V_{REF} / V_0 = 0.25$ , $V_0 = 0.7V$ to 2.688V                        |  |  |  |  |  |

|                     | 2'b11: $V_{REF} / V_0 = 0.125$ , $V_0 = 1.3V$ to 5.376V                       |  |  |  |  |  |

The MPQ8645P provides output voltage monitoring through the register READ VOUT (8Bh). To achieve the correct output voltage settina and monitorina. the reaisters VOUT\_COMMAND (21h), VOUT\_MARGIN\_ HIGH (25h), VOUT\_MARGIN\_LOW (26h), and VOUT\_SCALE\_LOOP (29h) should be set correspondingly. The steps below show how to set the output voltage to 2.5V.

- 1. Determine the Vo\_set source based on the OPERATION (01h) command. Assume that VOUT\_COMMAND (21h) is selected.

- Choose the D1[1:0] value based on the Vo\_set value. The D1[1:0] value is chosen so that the FB voltage is as close to 600mV as possible. In this case, both D1[1:0] = 2'b10 and D1[1:0] = 2'b11 can provide Vo = 2.5V, but D1[1:0] = 2'b10 yields a 625mV FB voltage, while D1[1:0] = 2'b11 yields a 312.5mV FB voltage. Choose D1[1:0] = 2'b10.

- 3. Set the VOUT\_SCALE\_LOOP (29h) to 0x00FA to match D1[1:0] = 2'b10.

- 4. Set the VOUT\_COMMAND (21h) to 0x4E2 (LSB = 2mV).

- 5. VOUT\_COMMAND (21h) must be sent after VOUT\_SCALE\_LOOP (29h) and D1h. Otherwise, the change of VOUT\_SCALE\_ LOOP (29h) and D1h will not be effective.

- 6. The VOUT\_COMMAND (21h) cannot exceed the minimum/maximum value specified in Table 2.

### Power Good (PGOOD)

The MPQ8645P has a power good (PGOOD) output. PGOOD is the open drain of a MOSFET. Connect PGOOD to VDRV or another external voltage source less than 3.6V through a pull-up resistor (typically 100k $\Omega$ ). After applying the input voltage, the MOSFET turns on so that PGOOD is pulled to GND before the soft start is ready. After the FB voltage reaches the threshold set by the PMBus command POWER\_GOOD\_ON and a delay set by the PMBus, PGOOD is pulled high. The delay can be chosen through the PMBus command MFR\_CTRL\_VOUT (D1h) [5:2].

When the converter encounters any fault (e.g. UV, OV, OT, UVLO, etc.), PGOOD is latched low. It cannot be pulled high again until a new soft start is initialized.

When the MPQ8645P is configured as the master in single- or multi-phase operation, the PG pin is used for fault indication. Therefore, PG must be pulled high to ensure proper operation. Otherwise, the MPQ8645P may enter protection response mode.

This slave fault detection feature can be enabled or disabled through the PMBus bit D0h[0].

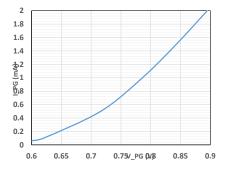

If the input supply fails to power the MPQ8645P, PGOOD is clamped low even though it is tied to an external DC source through a pull-up resistor. Figure 7 shows the relationship between the PGOOD voltage and the pull-up current.

Figure 7: PGOOD Clamped Voltage vs. Pull-Up Current

# **APPLICATION INFORMATION**

### Selecting the Input Capacitor

The step-down converter has a discontinuous input current, and requires a capacitor to supply AC current to the converter while maintaining the DC input voltage. Use ceramic capacitors for the best performance. During the layout, place the input capacitors as close to IN as possible.

The capacitance can vary significantly with temperature. Capacitors with X5R and X7R ceramic dielectrics are recommended because they are fairly stable over a wide temperature range.

The capacitors must have a ripple current rating that exceeds the converter's maximum input ripple current. Estimate the input ripple current with Equation (1):

$$I_{\text{CIN}} = I_{\text{OUT}} \times \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})}$$

(1)

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , calculated with Equation (2):

$$I_{CIN} = \frac{I_{OUT}}{2}$$

(2)

For simplification, choose an input capacitor with an RMS current rating that exceeds half the maximum load current.

The input capacitance value determines the converter input voltage ripple. Select a capacitor value that can meet any input voltage ripple requirements.

Estimate the input voltage ripple with Equation (3):

$$\Delta V_{\rm IN} = \frac{I_{\rm OUT}}{f_{\rm SW} \times C_{\rm IN}} \times \frac{V_{\rm OUT}}{V_{\rm IN}} \times (1 - \frac{V_{\rm OUT}}{V_{\rm IN}}) \quad (3)$$

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , calculated with Equation (4):

$$\Delta V_{IN} = \frac{1}{4} \times \frac{I_{OUT}}{f_{SW} \times C_{IN}}$$

(4)

## Selecting the Output Capacitor

The output capacitor maintains the DC output voltage. The output voltage ripple can be

estimated with Equation (5):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times (R_{\text{ESR}} + \frac{1}{8 \times f_{\text{SW}} \times C_{\text{OUT}}})$$

(5)

When using ceramic capacitors, the capacitance dominates the impedance at the switching frequency. Therefore, the output voltage ripple is dominated by the output capacitances. For simplification, estimate the output voltage ripple with Equation (6):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times f_{\text{SW}}^{2} \times L \times C_{\text{OUT}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \quad (6)$$

When using capacitors with a larger ESR (e.g. POSCAP, OSCON, etc.), the ESR dominates the impedance at the switching frequency. Therefore, the output voltage ripple can be determined by the ESR. For simplification, estimate the output ripple with Equation (7):

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}}) \times R_{ESR}$$

(7)

#### Selecting the Inductor

The inductor supplies constant current to the output load while being driven by the switching input voltage. A larger-value inductor results in less ripple current and a lower output ripple voltage, but also has a larger physical size, higher series resistance, and lower saturation current. Select an inductor value that sets the inductor peak-to-peak ripple current between 30% and 40% of the maximum switch current limit. Be sure to also design for a peak inductor current that is below the maximum switch current limit. Calculate the inductance value with Equation (8):

$$L = \frac{V_{OUT}}{f_{SW} \times \Delta I_{L}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(8)

Where  $\Delta I_{\text{L}}$  is the peak-to-peak inductor ripple current.

Choose an inductor that will not saturate under the maximum inductor peak current. The peak inductor current can be calculated with Equation (9):

$$I_{LP} = I_{OUT} + \frac{V_{OUT}}{2 \times f_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(9)

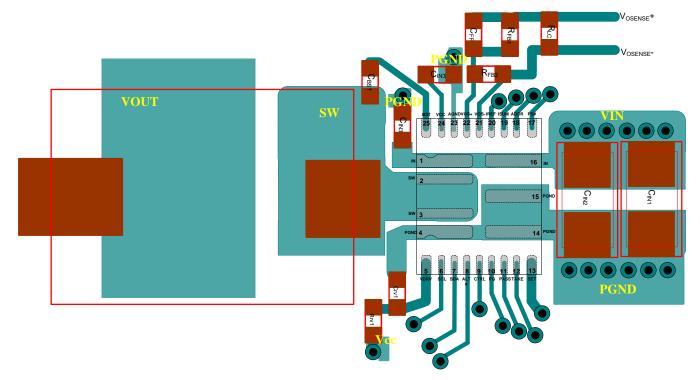

#### **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. For best performance, refer to Figure 8 and follow the guidelines below:

- 1. Place the input MLCC capacitors as close to the IN and PGND pins as possible.

- 2. Place one 1µF to 4.7µF 0402 MLCC near pin1.

- 3. Place the major MLCC capacitors on the same layer as the MPQ8645P.

- 4. Maximize the VIN and PGND copper plane to minimize parasitic impedance.

- 5. Place as many PGND vias as possible as close to the pin as possible to minimize parasitic impedance and thermal resistance.

- 6. Place a VCC decoupling capacitor close to the device.

- 7. Connect AGND and PGND at the point of the VCC capacitor's ground connection.

- 8. Place the BST capacitor as close to BST and SW as possible.

- 9. Use a trace width of 20 mils or higher to route the path (a  $0.1\mu$ F to  $1\mu$ F bootstrap capacitor is recommended).

- 10. Place a REF capacitor close to TRK/REF to RGND.

- 11. Place one 10pF to 100pF MLCC between the two remote sense lines.

Figure 8: Example of PCB Layout (Placement and Top Layer PCB)

# **PMBUS INTERFACE**

#### **PMBus Serial Interface Description**

The power management bus (PMBus) is an open-standard power management protocol that defines a means of communication with power conversion and other devices.

The PMBus is a two-wire, bidirectional serial interface, consisting of a data line (SDA) and a clock line (SCL). The lines are pulled to a bus voltage externally when they are idle. When connecting to the lines, a master device generates an SCL signal and device address, and arranges the communication sequence. This is based on I<sup>2</sup>C operation principles. The MPQ8645P is a PMBus slave that supports both standard mode (100kHz) and fast mode (400kHz and 1000kHz). The PMBus interface adds flexibility to the power supply solution.

#### **Slave Address**

To support multiple MPQ8645P devices used on the same PMBus, use the ADDR pin to program the slave address for each MPQ8645P device. There is 10µA of current flowing out of ADDR. Connect a resistor between ADDR and AGND to set the ADDR voltage. The internal ADC converts the pin voltage to set the PMBus address. A maximum of 32 addresses can be set via ADDR pin. Table 3 shows the PMBus address for different resistor values from ADDR AGND. Pre-set the register to MFR ADDR PMBUS (D3h) to set the PMBus address.

For multi-phase configurations, the slave phases can share the same address as the masters or have different addresses, depending on the application needs. The slave phases can only accept write commands, and cannot accept read commands from the PMBus master. The master phase can accept both write and read commands from the PMBus master.

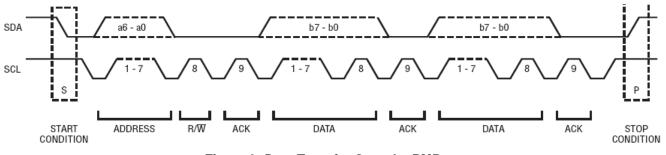

#### **Start and Stop Conditions**

The start and stop conditions are signaled by the master device, which signifies the beginning and end of the PMBus transfer. The start condition is defined as the SDA signal transitioning from high to low while the SCL is high. The stop condition is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 9).

| Table 3: PMBus Address | vs. ADDR Resistor |

|------------------------|-------------------|

|------------------------|-------------------|

| R <sub>ADDR</sub><br>(kΩ) | Slave Address<br>(R_IREF=60.4kΩ) | Slave Address<br>(R_IREF=180kΩ) |

|---------------------------|----------------------------------|---------------------------------|

| 4.99                      | 30h                              | 40h                             |

| 15                        | 31h                              | 41h                             |

| 24.9                      | 32h                              | 42h                             |

| 34.8                      | 33h                              | 43h                             |

| 45.3                      | 34h                              | 44h                             |

| 54.9                      | 35h                              | 45h                             |

| 64.9                      | 36h                              | 46h                             |

| 75                        | 37h                              | 47h                             |

| 84.5                      | 38h                              | 48h                             |

| 95.3                      | 39h                              | 49h                             |

| 105                       | 3Ah                              | 4Ah                             |

| 115                       | 3Bh                              | 4Bh                             |

| 124                       | 3Ch                              | 4Ch                             |

| 133                       | 3Dh                              | 4Dh                             |

| 147                       | 3Eh                              | 4Eh                             |

| 154                       | 3Fh                              | 4Fh                             |

The master then generates the SCL clocks and transmits the device address and the read/write direction bit (R/W) on the SDA line. Data is transferred in 8-bit bytes by the SDA line. Each byte of data is followed by an acknowledge bit (ACK).

#### **PMBus Update Sequence**

The MPQ8645P requires a start condition, a valid PMBus address, a register address byte, and a data byte for a single data update. The device acknowledges receipt of each byte by pulling the SDA line low during the high period of a single clock pulse. A valid PMBus address selects the MPQ8645P. The device performs an update on the falling edge of the LSB byte.

#### **Protocol Usage**

All PMBus transactions on the MPQ8645P are done using defined bus protocols. The following protocols are implemented:

- End byte with PEC

- Receive byte with PEC

- Write byte with PEC

- Read byte with PEC

- Write word with PEC

- Read word with PEC

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

• Block read with PEC

#### **PMBus Bus Message Format**

In the tables in Figure 10, unshaded cells indicate that the bus host is driving the bus actively, and shaded cells indicate that the MPQ8645P is driving the bus.

S = Start condition Sr = Repeated start condition P = Stop condition R = Read bit  $\overline{W}$  = Write bit A = Acknowledge bit (0)  $\overline{A}$  = Acknowledge bit (1)

"A" represents the acknowledge bit. The ACK bit is typically active low (logic 0) if the transmitted byte is received successfully by a device.

However, when the receiving device is the bus master, the acknowledge bit for the last byte read is a logic 1, indicated by  $\overline{A}$  (see Figure 9).

#### Packet Error Checking (PEC)

The MPQ8645P PMBus interface supports the use of the packet error-checking (PEC) byte. The PEC byte is transmitted by the MPQ8645P during a read transaction or sent by the bus host during a write transaction.

The PEC byte is used by the bus host or the MPQ8645P to detect errors during a bus transaction (depending on whether the transaction is a read or a write). If the host determines that the PEC byte read during a read transaction is incorrect, it can decide to repeat the read if necessary. If the MPQ8645P determines that the PEC byte sent during a

write transaction is incorrect, it ignores the command (does not execute it) and sets a status flag. Within a group command, the host can choose to send or not send a PEC byte as part of the message to the MPQ8645P.

#### PMBus Alert Response Address (ARA)

The PMBus alert response address (ARA) is a special address that can be used by the bus host to locate any devices that need to talk to it. A host typically uses a hardware interrupt pin to monitor the PMBus ALERT pins of a number of devices. When a host interruption occurs, the host issues a message on the bus using the PMBus receive byte, or the receive byte with PEC protocol.

The special address used by the host is 0x0C. Any devices that have a PMBus use the ALERT signal to return their own 7-bit address as the seven MSBs of the data byte. The LSB value is not used, and can be either 1 or 0. The host reads the device address from the received data byte, and proceeds to handle the alert condition.

More than one device may have an active PMBus ALERT signal and attempt to communicate with the host. In this case, the device with the lowest address dominates the bus and succeeds in transmitting its address to the host. The device that succeeds disables its PMBus alert signal. If the host sees that the PMBus alert signal is still low, it continues to read addresses until all devices that need to talk to it have successfully transmitted their addresses.

Figure 9: Data Transfer Over the PMBus

|          | and Duta and S     | ond        | Dist   |                                         |        |                  |          |                                   |

|----------|--------------------|------------|--------|-----------------------------------------|--------|------------------|----------|-----------------------------------|

| -        | end Byte and S     | ena i<br>1 | -      |                                         | 1      | 1                |          |                                   |

| 1<br>  S | /<br>Slave Address | Wr         | 1<br>A | Data Byte                               | 1<br>A | 1<br>P           |          |                                   |

| 1        | 7                  | 1          | 1      | 8                                       | 1      | 8                | 1        | 1                                 |

| s        | Slave Address      | 1 1        | A      | Data Byte                               | A      | PEC              | A        | P                                 |

|          |                    |            |        | -                                       |        | 120              |          |                                   |

|          | _ •                |            |        | e Byte with PEC                         |        |                  |          |                                   |

| 1<br>S   | 7<br>Slave Address | 1<br>Rd    | 1      | 8<br>Data Duta                          | 1<br>A | 1<br>P           |          |                                   |

| 1        | 7                  | 1          | A<br>1 | Data Byte<br>8                          |        |                  | 4        | 4                                 |

| S        | /<br>Slave Address | Rd         | A      | o<br>Data Byte                          | 1<br>A | 8<br>PEC         | 1<br>A   |                                   |

|          |                    |            |        | -                                       | ~      | TLO              | Α        |                                   |

| c) V     | /rite Byte and V   |            | Byt    |                                         |        |                  |          |                                   |

| 1        | 7                  | 1          | 1      | 8                                       | 1      | 8                | 1        |                                   |

| S        | Slave Address      | -          | A      | Command Code                            | A      | Data Byte        | A        | Р                                 |

| 1<br>S   | 7                  | 1          | 1      | 8                                       | 1      | 8<br>Data Duta   | 1        |                                   |

|          | Slave Address      | Wr         | Α      | Command Code                            | Α      | Data Byte        | Α        | PEC A P                           |

| d) V     | rite Word and      | Write      | W      | ord with PEC                            |        |                  |          |                                   |

| 1        | 7                  | 1          | 1      | 8                                       | 1      | 8                | 1        | 8 1 1                             |

| S        | Slave Address      | -          | Α      | Command Code                            | Α      | Data Byte Low    | Α        | Data Byte High A P                |

| 1        | 7                  | 1          | 1      | 8                                       | 1      | 8                | 1        | 8 1 8 1 1                         |

| S        | Slave Address      | Wr         | Α      | Command Code                            | Α      | Data Byte Low    | Α        | Data Byte High A PEC A P          |

| e) R     | ead Byte and R     | lead       | Byte   | e with PEC                              |        |                  |          |                                   |

| 1        | 7                  | 1          | 1      | 8                                       | 1      | 1 7              |          | 1 1 8 1 1                         |

| S        | Slave Address      | Wr         | А      | Command Code                            | А      | S Slave Addre    | SS       | Rd A Data Byte A P                |

| 1        | 7                  | 1          | 1      | 8                                       | 1      | 1 7              |          | <u> </u>                          |

| S        | Slave Address      | Wr         | А      | Command Code                            | А      | S Slave Addre    | ss       | Rd A Data Byte A PEC A P          |

| f) D     | ead Word and F     | Pood       | Wo     | rd with DEC                             |        | I I              |          |                                   |

| 1        |                    | 1          | 1      | 8                                       | 1      | 1 7              |          | 1 1 8 1                           |

| s        | Slave Address      | Wr         | A      | Command Code                            | A      | S Slave Addre    | SS       | Rd A Data Byte Low A              |