# HR1200

# High-Performance Digital PFC+LLC Combo Controller

NOT RECOMMENDED FOR NEW DESIGNS. REFER TO HR1203

#### DESCRIPTION

The HR1200 is a high-performance controller that integrates an advanced digital PFC controller and a half-bridge LLC resonant controller. It requires quite low input power at no load or ultra-light load, making it compliant with Energy using Product Directive (EuP) Lot 6 and Code of Conduct Version 5 Tier 2 specifications.

The PFC of the HR1200 employs a patented average current control scheme, which can operate both in continuous conduction mode (CCM) and discontinuous conduction mode (DCM) according to the instantaneous condition of the input voltage and output load. The IC exhibits excellent efficiency and high power factor (PF) at light load. In CCM, the HR1200 can be used in applications up to 500W with minimal board size limitations. The performance of the PFC can be optimized by programming multiple parameters through an I<sup>2</sup>C GUI. Programming can be completed either by the factory or by the customer referring to a detailed user guide.

The half-bridge LLC resonant converter achieves high efficiency with zero-voltage switching (ZVS). The HR1200 implements an adaptive dead-time adjustment (ADTA) function to guarantee ZVS in different load conditions. Additionally, the HR1200 can prevent the LLC converter from operating in capacitive mode, making it more robust and easier to design.

The HR1200 integrates a high-voltage (HV) current source internally for start-up. When the AC input is removed, the HV current source also functions as an X-cap discharger. Such features are helpful to reduce related devices, thus reduce power consumption at no load.

The HR1200 has multiple protection features including thermal shutdown (TSD), open-loop protection (OLP), over-current protection (OCP), over-voltage protection (OVP), and brown-in/brown-out protection.

#### **FEATURES**

#### **General System Features**

- Meets EuP Lot 6 and COC Version 5 Tier 2 Specifications

- HV Current Source for Start-Up

- Smart X-Cap Discharger

- Standard I<sup>2</sup>C Interface

- 1k EEPROM to Store Parameters

- User-Friendly GUI for Digital PFC

#### **PFC Controller**

- High Efficiency from Light Load to Full Load by CCM/DCM Multi-Mode Control

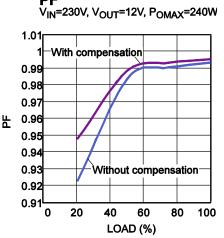

- High PF Due to Patented Input Capacitor Current Compensation

- Programmable Frequency Jittering

- Programmable Brown-In and Brown-Out

- Programmable Soft Start

- Cycle-by-Cycle Current Limit

- Open-Loop Protection

#### LLC Controller

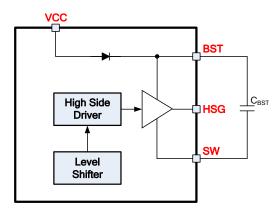

- 600V High-Side Gate Driver with Integrated Bootstrap Diode and High dv/dt Immunity

- Adaptive Dead-Time Adjustment of HB LLC with Minimum and Maximum Limit

- Burst Mode Switching

- Safe Start-Up in Case of System Fault

- Two-Level Over-Current Protection (OCP)

- Latch Shutdown Protection

- Over-Temperature Protection (OTP)

- Capacitive Mode Protection

#### **APPLICATIONS**

- Notebook Adapters

- All-in-One or Gaming Power Supply

- Desktop PC and ATX Power

- General AC/DC Power Supply up to 600W

- LCD TV and Plasma TV Power Supply

MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under quality assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

Analog digital adaptive modulation (ADAM) and advanced asynchronous mode (AAM) are trademarks of Monolithic Power Systems, Inc.

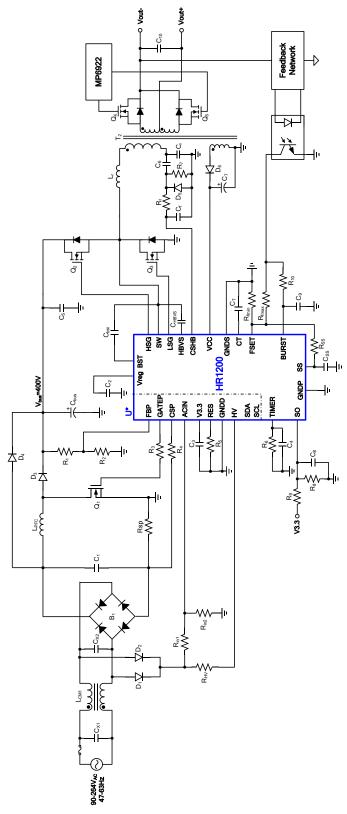

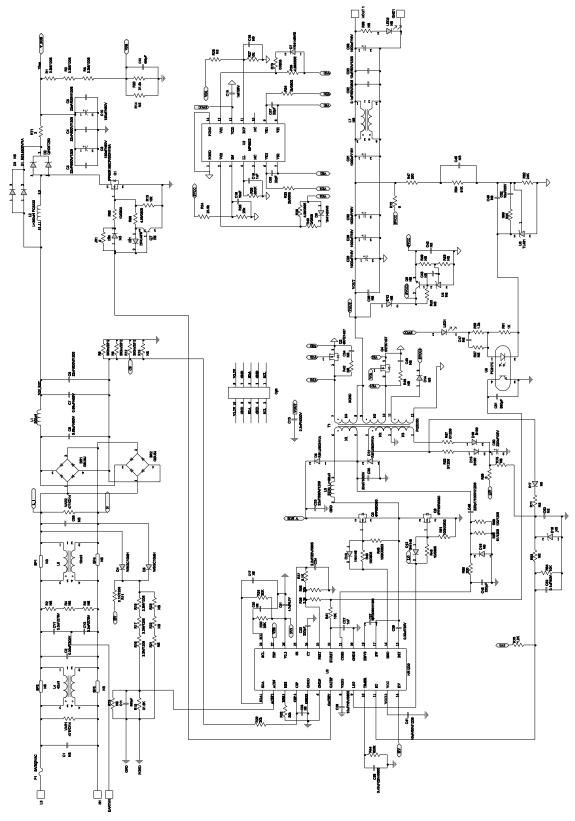

# **TYPICAL APPLICATION**

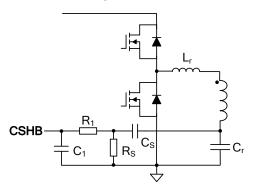

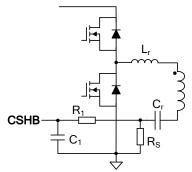

**Figure 1: Typical Application**

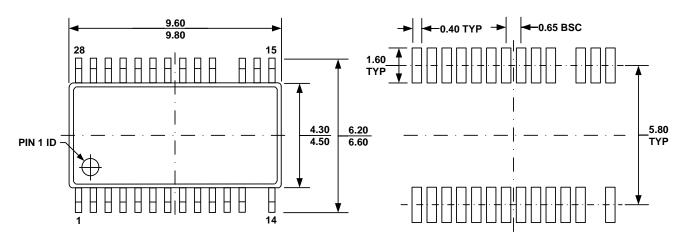

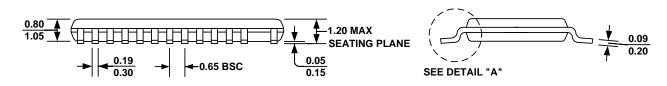

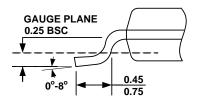

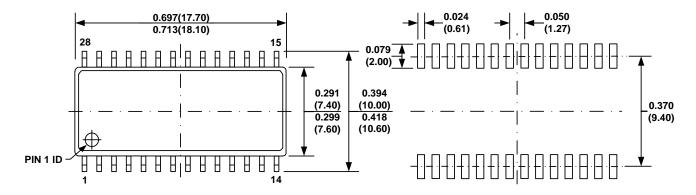

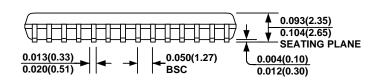

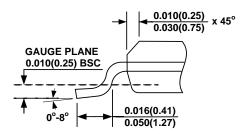

#### ORDERING INFORMATION

| Part Number*   | Package  | Top Marking |

|----------------|----------|-------------|

| HR1200GM-XXXX* | TSSOP-28 | See Below   |

| HR1200GY-XXXX* | SOIC-28  | See Below   |

\*-XXXX: internal code version control.

For customer-specific projects, MPS will assign a special 4-digit number.

For Tape & Reel, add suffix -Z (e.g. HR1200GM-XXXX-Z)

For Tape & Reel, add suffix -Z (e.g. HR1200GY-XXXX-Z)

#### **TOP MARKING**

# M<u>PSYYWW</u> HR1200 LLLLLLLL

MPS: MPS prefix YY: year code WW: week code

HR1200: first six digits of the part number

LLLLLLL: lot number

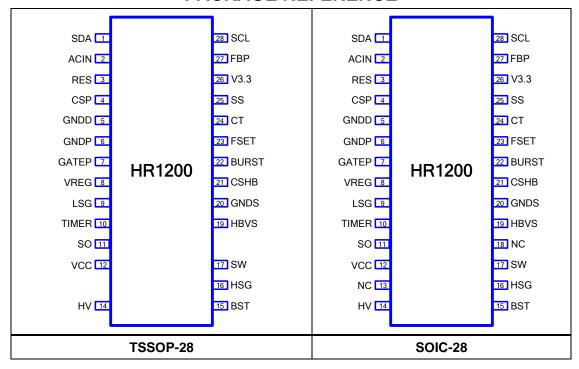

#### PACKAGE REFERENCE

| Recommended Operating Condition      | ons <sup>(1)</sup> | Thermal Resistance <sup>(4)</sup> | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |       |

|--------------------------------------|--------------------|-----------------------------------|-------------------------|--------------------------|-------|

| HV <sub>pk</sub>                     | . ≤500V            | TSSOP-28                          | 82                      | 20                       | .°C/W |

| Supply voltage (V <sub>CC</sub> )14\ | / to 30V           | SOIC-28                           | 60                      | 30                       | .°C/W |

| Operating junction temp40°C to       | +125°C             |                                   |                         |                          |       |

# **ABSOLUTE MAXIMUM RATINGS**(2)

| Parameter                              | Symbol               | Condition                | Min  | Max          | Units |

|----------------------------------------|----------------------|--------------------------|------|--------------|-------|

| General                                |                      |                          |      |              |       |

| Total power dissipation <sup>(3)</sup> | P <sub>total</sub>   | T <sub>amb</sub> = 125°C |      | 1.56         | W     |

| Storage temperature                    | T <sub>stg</sub>     |                          | -55  | +150         | °C    |

| Junction temperature                   | TJ                   |                          | -40  | +150         | °C    |

| Lead temperature                       | T <sub>LEAD</sub>    |                          |      | 260          | °C    |

| Voltage                                |                      |                          |      |              |       |

| Voltage on HV                          | V <sub>HV</sub>      | Continuous               | -0.5 | +700         | V     |

| Floating supply voltage                | V <sub>BST</sub>     |                          | -1   | +618         | V     |

| Floating ground voltage                | Vsw                  |                          | -3   | +618         | V     |

| Voltage on high-side gate driver       | V <sub>HSG</sub>     |                          |      | +618         | V     |

| Floating ground max. slew rate         | dVsw/dt              |                          |      | 50           | V/ns  |

| Voltage on VCC                         | Vcc                  |                          | -0.5 | +38          | V     |

| Voltage on VREG                        | V <sub>reg</sub>     |                          | -0.5 | +14          | V     |

| VREG Supply Current                    | I <sub>reg</sub>     |                          |      | 50           | mA    |

| V3.3 Supply Current                    | I <sub>3V3</sub>     |                          |      | 20           | mA    |

| Voltage on low-side gate driver        | $V_{LSG}$            |                          | -0.5 | +14          | V     |

| Voltage on PFC gate driver             | V <sub>PFCG</sub>    |                          | -0.5 | +14          | V     |

| Voltage on CS                          | Vcs                  |                          | -6.5 | +6.5         | V     |

| Voltage on HBVS                        | V <sub>HBVS</sub>    |                          | -0.3 | Self-limited | V     |

| Other analog pins                      |                      |                          | -0.5 | 6.5          | V     |

| Other digital pins                     |                      |                          | -0.5 | 2            | V     |

| Analog ground to digital ground        | GNDP/GNDS<br>to GNDD |                          | -0.3 | +0.3         | V     |

| Current                                |                      |                          |      |              |       |

| Current on HBVS                        | I <sub>HBVS</sub>    |                          | -65  | +65          | mΑ    |

| Source current of FSET                 | I <sub>FSET</sub>    |                          |      | 2            | mΑ    |

| ESD <sup>(4)</sup>                     |                      |                          |      |              |       |

|                                        | All pins             | Human body model         |      | 2000         | V     |

|                                        | All pins             | Machine model            |      | 200          | V     |

|                                        | All pins             | Charged device model     |      | 500          | V     |

#### NOTES:

- 1) The device is not guaranteed to function outside of its operating conditions.

- Exceeding these ratings may damage the device.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 4) Measured on JESD51-7, 4-layer PCB.

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 25V,  $T_J$  = -40°C to 125°C, currents entering the IC are positive, min and max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| Parameter                                                  | Symbol                   | Condition                                                               | Min  | Тур  | Max  | Units |

|------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------|------|------|------|-------|

| High-Voltage Start-Up Current Source (HV                   | <u>/)</u>                |                                                                         | •    | •    | •    | •     |

| Breakdown voltage                                          | $V_{HVBR}$               |                                                                         | 700  |      |      | V     |

| Normal charge current                                      | Ihvnor                   | V <sub>HV</sub> = 100V, V <sub>CC</sub> = 15V,<br>T <sub>J</sub> = 25°C | 5.5  | 7    | 8.5  | mA    |

| Normal charge current                                      | I <sub>HVNOR</sub>       | V <sub>HV</sub> = 100V, V <sub>CC</sub> = 15V                           | 4.5  | 7    | 8.9  | mA    |

| Supply current when fault occurs                           | I <sub>HVLimit</sub>     | V <sub>HV</sub> = 100V, V <sub>CC</sub> = 0V                            | 0.8  | 1.4  | 2.1  | mA    |

| Leakage current when turned off                            | I <sub>HVoff</sub>       | $V_{HV} = 400V, V_{CC} = 24V$                                           |      | 7    | 10   | μA    |

| IC Power Supply (VCC)                                      |                          |                                                                         | •    | •    | •    | •     |

| IC turn-on threshold voltage when HV is detected           | V <sub>CCON(HV)</sub>    | V <sub>HV</sub> > V <sub>HVON</sub>                                     | 20   | 21.5 | 23.1 | V     |

| UV protection threshold 1                                  | V <sub>CCUVP1</sub>      | LLC operation                                                           | 10.5 | 11.3 | 12.1 | V     |

| UV protection threshold 2 <sup>(5)</sup>                   | V <sub>CCUVP2</sub>      | LLC disabled                                                            | 13.9 | 15   | 16.2 | V     |

| IC release threshold                                       | Vccrst                   |                                                                         | 8.4  | 9    | 9.9  | V     |

| Operation current at normal                                | I <sub>CC(nor)</sub>     | $R_{RES}$ = 20k $\Omega$<br>$f_{PFC}$ = 120kHz<br>$f_{LLC}$ = 200kHz    |      | 14   |      | mA    |

| Start-up current                                           | ICC-start1               | Vcc = 20V                                                               |      | 0.55 | 0.7  | mA    |

| Current at fault (LLC fault, PFC operation) <sup>(5)</sup> | ICC-Disable1             | TIMER = 4V<br>PFC burst                                                 |      | 2    |      | mA    |

| Current at fault (LLC fault, PFC fault) <sup>(5)</sup>     | I <sub>CC-Disable2</sub> | TIMER = 4V                                                              |      | 0.5  |      | mA    |

| Regulated Power Supply (VREG)                              |                          |                                                                         |      |      |      |       |

| Regulated output voltage                                   | $V_{reg}$                | $I_{reg} = 0mA$                                                         | 11.3 | 12   | 12.8 | V     |

| Regulated output voltage                                   | <b>V</b> reg             | $I_{reg} = 30mA$                                                        | 10.8 | 11.8 | 12.6 | V     |

| IC enable threshold                                        | $V_{regON}$              |                                                                         | 10.2 | 10.8 | 11.5 | V     |

| UVP                                                        | $V_{\text{regUVP}}$      |                                                                         | 7.7  | 8.2  | 8.8  | V     |

| Power Supply for Digital Core (V3.3)                       |                          |                                                                         |      |      |      |       |

| Voltage regulation range                                   | V <sub>3V3</sub>         | $I_{3V3} = 0mA$                                                         | 2.95 | 3.15 | 3.45 | V     |

| Voltage regulation range                                   | <b>V</b> 3V3             | $I_{3V3} = 15mA$                                                        | 2.85 | 3.1  | 3.35 | V     |

| X-Cap Discharger (HV)                                      |                          |                                                                         |      |      |      |       |

| X-cap discharger current <sup>(5)</sup>                    | I <sub>X-d</sub>         |                                                                         |      | 5.5  |      | mA    |

| X-cap discharger clock time                                | T <sub>X-d</sub>         |                                                                         | 0.9  | 1.5  | 2.4  | ms    |

| PFC Gate Driver                                            |                          |                                                                         |      |      |      |       |

| Sourcing capacity <sup>(5)</sup>                           | I <sub>gate_sr</sub>     | C <sub>Gate</sub> = 1nF                                                 |      | 750  |      | mA    |

| Sinking capacity <sup>(5)</sup>                            | I <sub>gate_sk</sub>     | C <sub>Gate</sub> = 1nF                                                 |      | -800 |      | mA    |

| Cata an register                                           | Ron(H)                   | Sourcing 20mA                                                           |      | 4.5  |      | Ω     |

| Gate-on resistor                                           | Ron(L)                   | Sinking 20mA                                                            |      | 2.5  |      | Ω     |

| Voltage fall time                                          | T <sub>f</sub>           | C <sub>Gate</sub> = 1nF                                                 |      | 10   |      | ns    |

| Voltage rise time                                          | $T_r$                    | C <sub>Gate</sub> = 1nF                                                 |      | 15   |      | ns    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{\text{CC}}$  = 25V,  $T_{\text{J}}$  = -40°C to 125°C, currents entering the IC are positive, min and max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| Parameter                                       | Symbol                 | Condition                  | Min   | Тур   | Max   | Units |

|-------------------------------------------------|------------------------|----------------------------|-------|-------|-------|-------|

| Reference Current (RES)                         | •                      |                            | •     | •     | •     |       |

| Voltage regulation range                        | $V_{RT}$               | T <sub>J</sub> = 25°C      | 1.245 | 1.25  | 1.255 | V     |

| System Clock                                    | ·                      |                            |       |       |       |       |

| Ola ala fas accessor                            | f <sub>osc_nor</sub>   | At normal                  |       | 19    |       | MHz   |

| Clock frequency                                 | f <sub>osc_nopwm</sub> | At fault or burst off      |       | 1     |       | MHz   |

| AC Input Sensing (ACIN)                         |                        |                            |       |       |       |       |

| Voltage range                                   |                        | K <sub>ACIN</sub> = 0.0032 | 0     |       | 1.6   | V     |

| PFC Feedback (FBP)                              |                        |                            |       |       |       |       |

| Voltage range                                   |                        | K <sub>ACIN</sub> = 0.0032 | 0     |       | 1.6   | V     |

| Current Sense (CSP)                             | ·                      |                            |       |       |       |       |

| Voltage range                                   |                        | K <sub>ACIN</sub> = 0.0032 | 0     |       | 1.6   | V     |

| Bias current in CSP                             | I <sub>csp-bias</sub>  | $R_{RES} = 20k\Omega$      | 61    | 62.5  | 64    | μA    |

| ADC for ACIN, FB, and CSP                       |                        |                            |       |       |       |       |

| ADC voltage reference                           |                        | T <sub>J</sub> = 25°C      | 1.593 | 1.600 | 1.607 | V     |

| ADC resolution <sup>(6)</sup>                   |                        |                            |       | 10    |       | bits  |

| Acquisition time <sup>(6)</sup>                 |                        |                            |       |       | 350   | ns    |

| Integral non-linearity (INL) <sup>(6)</sup>     |                        |                            |       | ±7.0  |       | LSB   |

| Differential non-linearity (DNL) <sup>(6)</sup> |                        |                            |       | ±4.5  |       | LSB   |

| Offset error <sup>(6)</sup>                     |                        |                            |       | ±0.5  |       | LSB   |

| Gain error <sup>(6)</sup>                       |                        |                            |       | ±1.5  |       | LSB   |

| DAC for OVP and OCL                             |                        |                            |       |       |       |       |

| Reference voltage                               |                        | T <sub>J</sub> = 25°C      | 1.593 | 1.600 | 1.607 | V     |

| Resolution <sup>(6)</sup>                       |                        |                            |       | 7     |       | bits  |

| Integral non-linearity (INL) <sup>(6)</sup>     |                        |                            |       | ±1.5  |       | LSB   |

| Differential non-linearity (DNL) <sup>(6)</sup> |                        |                            |       | ±0.3  |       | LSB   |

| Offset error <sup>(6)</sup>                     |                        |                            |       | ±0.2  |       | LSB   |

| Gain error <sup>(6)</sup>                       |                        |                            |       | ±1.5  |       | LSB   |

| Output setting time <sup>(5)</sup>              |                        |                            |       | 5     |       | μs    |

| DAC for Set Comparator                          |                        |                            |       |       |       |       |

| Reference voltage                               |                        | T <sub>J</sub> = 25°C      | 1.593 | 1.600 | 1.607 | V     |

| Resolution <sup>(6)</sup>                       |                        |                            |       | 10    |       | bits  |

| Integral non-linearity (INL) <sup>(6)</sup>     |                        |                            |       | ±4.5  |       | LSB   |

| Differential non-linearity (DNL) <sup>(6)</sup> |                        |                            |       | ±2.0  |       | LSB   |

| Offset error <sup>(6)</sup>                     |                        |                            |       | ±0.5  |       | LSB   |

| Gain error <sup>(6)</sup>                       |                        |                            |       | ±1.5  |       | LSB   |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{\text{CC}}$  = 25V,  $T_{\text{J}}$  = -40°C to 125°C, currents entering the IC are positive, min and max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| Parameter                                                 | Symbol                | Condition                                                     | Min      | Тур  | Max  | Units |

|-----------------------------------------------------------|-----------------------|---------------------------------------------------------------|----------|------|------|-------|

| Comparator for Set Signal, OVP, and O                     | CL                    |                                                               | •        |      | •    | •     |

| Offset voltage                                            |                       |                                                               |          | 60   | 360  | mV    |

| I <sup>2</sup> C Characteristics (SCL/SDA) <sup>(5)</sup> |                       | 1                                                             |          |      | l    | l     |

| Input high voltage (VIH)                                  |                       |                                                               | 2.1      |      |      | V     |

| Input low voltage (VIL)                                   |                       |                                                               |          |      | 0.8  | V     |

| Output low voltage (VOL)                                  |                       |                                                               |          |      | 0.4  | V     |

| I <sup>2</sup> C Timing Characteristics <sup>(5)</sup>    | <b></b>               |                                                               | <b>J</b> | JI.  |      | l .   |

| Operating frequency range                                 |                       |                                                               |          | 100  | 400  | kHz   |

| Bus free time                                             |                       | Between stop and start                                        | 4.7      |      |      | μs    |

| Holding time                                              |                       |                                                               | 4.0      |      |      | μs    |

| Repeated start condition setup time                       |                       |                                                               | 4.7      |      |      | μs    |

| Stop condition setup time                                 |                       |                                                               | 4.0      |      |      | μs    |

| Data hold time                                            |                       |                                                               | 0        |      |      | ns    |

| Data setup time                                           |                       |                                                               | 250      |      |      | ns    |

| Clock low time out                                        |                       |                                                               | 25       |      | 35   | ms    |

| Clock low period                                          |                       |                                                               | 4.7      |      |      | μs    |

| Clock high period                                         |                       |                                                               | 4.0      |      | 50   | μs    |

| Clock/Data fall time                                      |                       |                                                               |          |      | 300  | ns    |

| Clock/Data rise time                                      |                       |                                                               |          |      | 1000 | ns    |

| High-Side Floating Gate Driver Supply (                   | (BST, SW)             |                                                               |          |      |      |       |

| BST leakage current                                       | ILKBST                | V <sub>BST</sub> = 600V                                       |          |      | 10   | μA    |

| SW leakage current                                        | I <sub>LKSW</sub>     | Vsw = 582V                                                    |          |      | 10   | μA    |

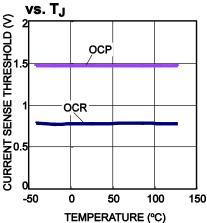

| Current Sensing of the Half-Bridge (CS                    | HB)                   |                                                               |          |      |      |       |

| Frequency shift threshold                                 | Vcs-ocr               | OCR                                                           | 0.7      | 0.77 | 0.83 | V     |

| OCP threshold                                             | Vcs-ocp               | OCP                                                           | 1.41     | 1.48 | 1.55 | V     |

| Current polarity comparator reference when HSG is on      | VCSPR                 |                                                               |          | 80   |      | mV    |

| Current polarity comparator reference when LSG is on      | V <sub>CSNR</sub>     |                                                               |          | -80  |      | mV    |

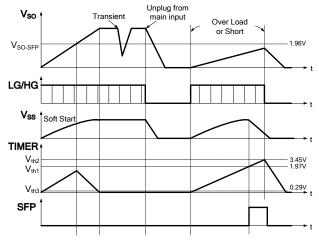

| Output Voltage Sense (SO)                                 |                       |                                                               | •        | •    | •    |       |

| Latch protection on SO                                    | V <sub>SO-Latch</sub> |                                                               | 3.22     | 3.42 | 3.6  | V     |

| Start-up failure protection on SO                         | $V_{\text{SO-SFP}}$   |                                                               | 1.85     | 1.96 | 2.08 | V     |

| Pull-up current on SO                                     | Iso-PU                |                                                               |          | 100  |      | nA    |

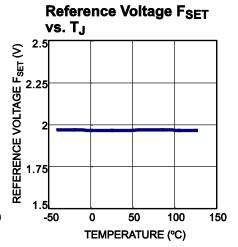

| Oscillator (FSET, CT)                                     | •                     |                                                               | •        | •    | •    | •     |

| Outrot data souls                                         |                       | T <sub>J</sub> = 25°C                                         | 48       | 50   | 52   | %     |

| Output duty cycle                                         | D                     | $T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | 47       | 50   | 53   | %     |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{\text{CC}}$  = 25V,  $T_{\text{J}}$  = -40°C to 125°C, currents entering the IC are positive, min and max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| Parameter                                           | Symbol                | Condition                                                       | Min  | Тур  | Max  | Units |

|-----------------------------------------------------|-----------------------|-----------------------------------------------------------------|------|------|------|-------|

| Oscillation frequency                               | f <sub>osc</sub>      |                                                                 |      |      | 600  | kHz   |

| CT peak value                                       | V <sub>СТР</sub>      |                                                                 | 3.54 | 3.74 | 3.94 | V     |

| CT valley value                                     | Vстv                  |                                                                 | 0.79 | 0.87 | 0.95 | V     |

| Voltage reference at FSET                           | V <sub>REF</sub>      |                                                                 | 1.88 | 1.97 | 2.06 | V     |

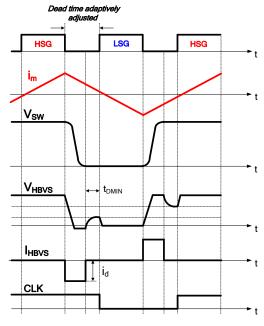

| Dead time                                           | t <sub>DMIN</sub>     | C <sub>HBVS</sub> = 5pF                                         |      | 240  |      | ns    |

| Dead time                                           | t <sub>DMAX</sub>     |                                                                 | 0.82 | 1.1  | 1.38 | μs    |

| Timer for CMP                                       | t <sub>D_float</sub>  | HBVS floating                                                   | 230  | 300  | 390  | ns    |

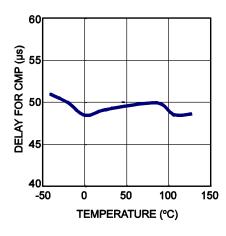

| Timor for Own                                       | td_cmp                |                                                                 |      | 50   |      | μs    |

| Half-Bridge Voltage Sensing (HBVS)                  |                       |                                                                 |      |      |      |       |

| Voltage clamp                                       | V <sub>HBVS-C</sub>   |                                                                 |      | 7.5  |      | V     |

| Minimum voltage for the change rate to be detected  | dv <sub>min</sub> /dt | С <sub>нвуѕ</sub> = 5pF, typically                              |      |      | 190  | V/µs  |

| Turn-on delay                                       | T <sub>d</sub>        | Slope finish to turn-on delay                                   |      | 130  |      | ns    |

| Soft-Start Function (SS)                            |                       |                                                                 |      |      |      |       |

| Discharge resistance                                | Rd                    | Vcs > Vcs-ocr                                                   |      | 120  |      | Ω     |

| Threshold for OCP                                   | Vss-ocp               | Vcs > Vcs-ocp                                                   | 1.61 | 1.72 | 1.82 | V     |

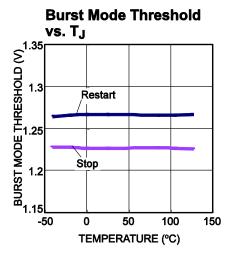

| Standby Function (BURST)                            |                       |                                                                 |      |      |      |       |

| Disable threshold                                   | V <sub>th</sub>       |                                                                 | 1.18 | 1.23 | 1.28 | V     |

| Hysteresis                                          | V <sub>hys</sub>      |                                                                 |      | 40   |      | mV    |

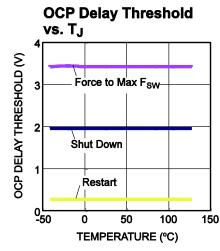

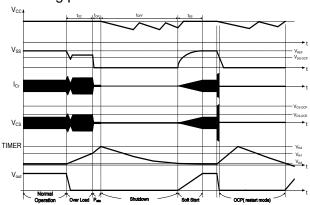

| Delayed Shutdown (TIMER)                            |                       |                                                                 |      |      |      |       |

| Charge current                                      | Icharge               | V <sub>TIMER</sub> = 1V,<br>V <sub>CS</sub> = 0.85V,<br>SO = 3V | 90   | 140  | 180  | μA    |

| Charge current for SFP                              | ICHARGE_SFP           | SO < 2.5V                                                       |      | 25   |      | μA    |

| Threshold for forced operation at maximum frequency | $V_{th1}$             |                                                                 | 1.87 | 1.97 | 2.07 | V     |

| Shutdown threshold                                  | $V_{th2}$             |                                                                 | 3.25 | 3.45 | 3.65 | V     |

| Restart threshold                                   | V <sub>th3</sub>      |                                                                 | 0.23 | 0.29 | 0.35 | V     |

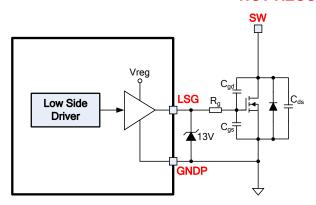

| Low-Side Gate Driver (LSG)                          | l                     |                                                                 |      |      | I    |       |

| Peak source current <sup>(5)</sup>                  | Isourcepk             |                                                                 |      | 0.75 |      | Α     |

| Peak sink current <sup>(5)</sup>                    | I <sub>sinkpk</sub>   |                                                                 |      | 0.87 |      | Α     |

| Sourcing resistor                                   | R <sub>source</sub>   |                                                                 |      | 4    |      | Ω     |

| Sinking resistor                                    | Rsink                 |                                                                 |      | 2    |      | Ω     |

| Fall time                                           | t <sub>f</sub>        |                                                                 |      | 20   |      | ns    |

| Rise time                                           | tr                    |                                                                 |      | 20   |      | ns    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{CC}$  = 25V,  $T_J$  = -40°C to 125°C, currents entering the IC are positive, min and max are guaranteed by characterization, typical is tested under 25°C, unless otherwise specified.

| Parameter                             | Symbol              | Condition | Min | Тур  | Max | Units |

|---------------------------------------|---------------------|-----------|-----|------|-----|-------|

| High-Side Gate Driver (HSG, Reference | d to SW)            |           |     |      |     |       |

| Peak source current <sup>(5)</sup>    | Isourcepk           |           |     | 0.74 |     | Α     |

| Peak sink current <sup>(5)</sup>      | İsinkpk             |           |     | 0.87 |     | Α     |

| Sourcing resistor                     | R <sub>source</sub> |           |     | 4    |     | Ω     |

| Sinking resistor                      | R <sub>sink</sub>   |           |     | 2    |     | Ω     |

| Fall time                             | t <sub>f</sub>      |           |     | 20   |     | ns    |

| Rise time                             | t <sub>r</sub>      |           |     | 20   |     | ns    |

| Thermal Shutdown                      |                     |           |     |      |     |       |

| Thermal shutdown threshold            |                     |           |     | 145  |     | °C    |

| Thermal shutdown recovery threshold   |                     |           |     | 100  |     | °C    |

#### NOTE:

- 5) Guaranteed by design.

- 6) Guaranteed by characterization.

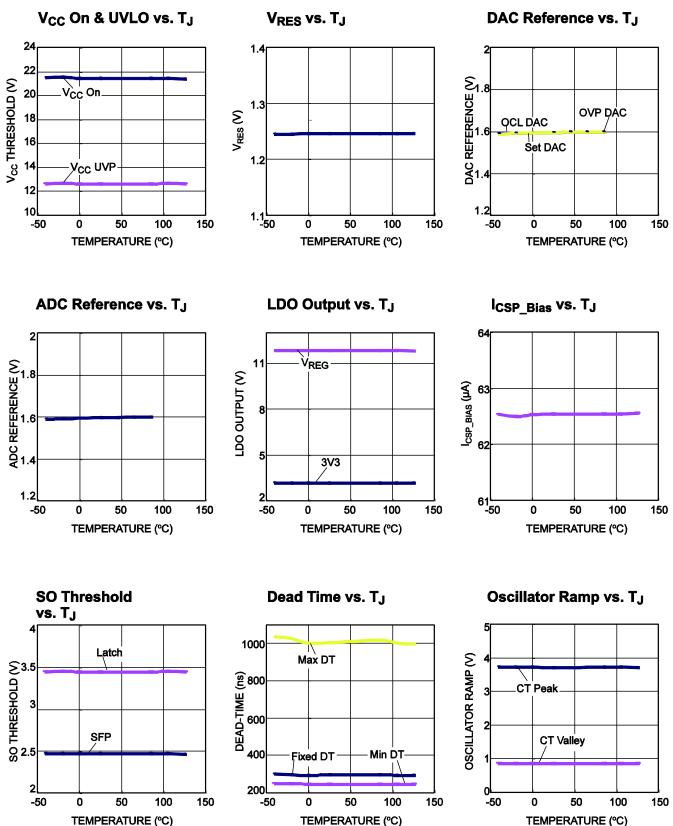

#### TYPICAL CHARACTERISTICS

# TYPICAL CHARACTERISTICS (continued)

#### Delay for CMP vs. TJ

## **Current Sense Threshold**

88 0

20

#### NOT RECOMMENDED FOR NEW DESIGNS. REFER TO HR1203

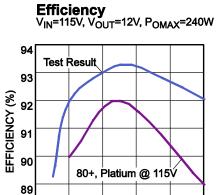

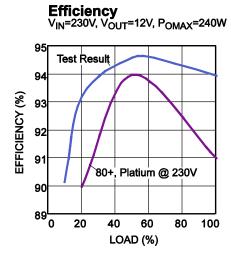

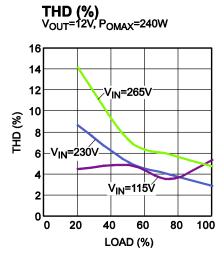

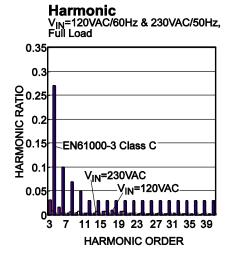

#### TYPICAL PERFORMANCE CHARACTERISTICS

100

80

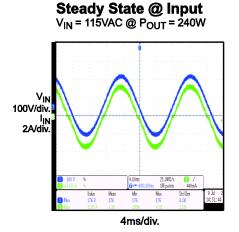

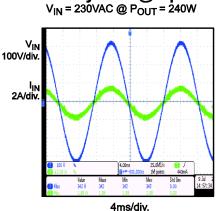

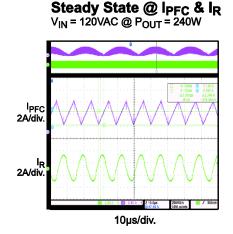

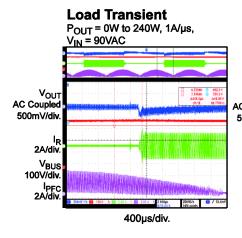

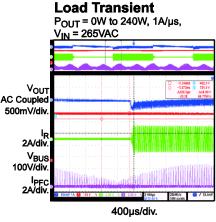

$V_{IN}$  = 85V to 265V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 20A,  $T_A$  = 25°C, unless otherwise noted.

40

60

LOAD (%)

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

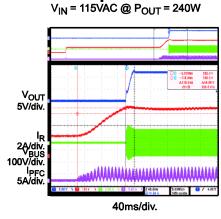

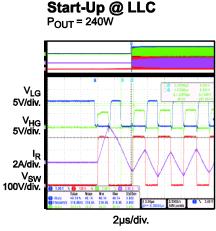

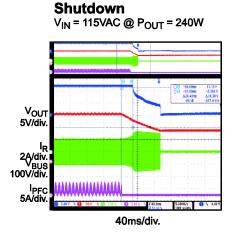

$V_{IN}$  = 85V to 265V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 20A,  $T_A$  = 25°C, unless otherwise noted.

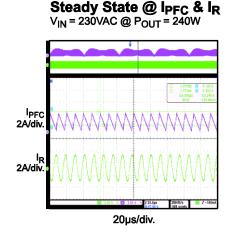

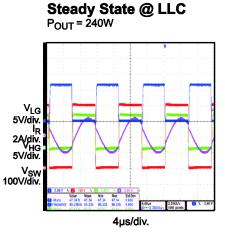

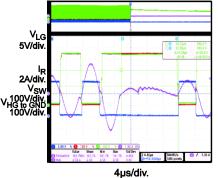

Steady State @ Input

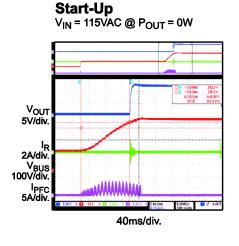

Start-Up

**ADTA**

#### NOT RECOMMENDED FOR NEW DESIGNS. REFER TO HR1203

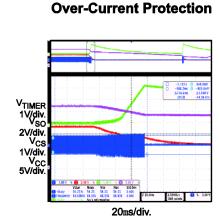

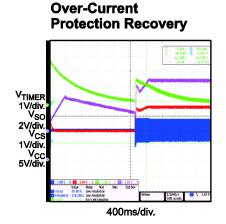

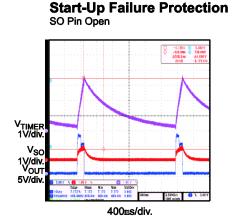

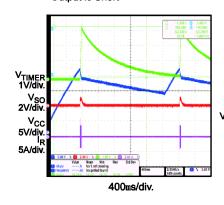

#### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 85V to 265V,  $V_{OUT}$  = 12V,  $I_{OUT}$  = 20A,  $T_A$  = 25°C, unless otherwise noted.

# VLG 5V/div. VHBVS 2V/div. VHBVS 2V/div. VHSVS 100V/div. VHSVS

# **Start-Up Failure Protection** Output is Short

## **Capacitive Mode Protection**

© 2020 MPS. All Rights Reserved.

# **PIN FUNCTIONS**

| Package<br>Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | SDA   | I <sup>2</sup> C data bus. Connect a suitable pull-up resistor from SDA to V3.3.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2                | ACIN  | <b>Input voltage sensing.</b> ACIN is connected to ADC internally. The voltage is used for on-time calculation and brown-in/brown-out protection. The ratio of the external resistor divider should be 0.0032. It is recommended to connect a 680pF capacitor from ACIN to GNDD.                                                                                                                                                                                                     |

| 3                | RES   | Reference current for producing system clock and bias voltage on CSP. RES connects to a precise reference voltage of 1.25V internally. The reference current is produced by connecting a $20k\Omega$ , $0.5\%$ resistor externally from RES to GNDD.                                                                                                                                                                                                                                 |

| 4                | CSP   | Sensing of the PFC inductor current. Connect a $20k\Omega$ , 0.5% resistor to CS to produce a bias voltage of 1.25V.                                                                                                                                                                                                                                                                                                                                                                 |

| 5                | GNDD  | Ground reference for the digital core of the PFC.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6                | GNDP  | Ground reference of the PFC gate driver and the LLC low-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7                | GATEP | Gate driver output of the PFC MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8                | VREG  | <b>Regulated power supply.</b> VREG provides a regulated power supply for the PFC and LLC gate drivers or external circuits.                                                                                                                                                                                                                                                                                                                                                         |

| 9                | LSG   | <b>Low-side gate driver of HB.</b> The driver is capable of a minimum 0.7A sourcing current and a minimum 0.8A peak sinking current to drive the lower MOSFET of the half-bridge leg. LSG is actively tied to GND during UVLO.                                                                                                                                                                                                                                                       |

| 10               | TIMER | Setting of protection and recovery time. Connect a capacitor and a resistor from TIMER to GNDS to set both over-current protection delay and recovery delay.                                                                                                                                                                                                                                                                                                                         |

| 11               | SO    | <b>Latch function for OVP and OTP.</b> If the SO voltage exceeds $V_{\text{SO-Latch}}$ , the IC stops switching immediately and remains latched off until VCC drops below $V_{\text{CCRST}}$ . When the LLC is enabled during start-up, if the SO voltage is still below $V_{\text{SO-SFP}}$ after the TIMER voltage reaches $V_{\text{th2}}$ , the IC stops operating. Connect SO and GNDS with a noise-decoupling capacitor more than 100nF placed as close to the IC as possible. |

| 12               | VCC   | <b>IC supply power.</b> When the power is on, VCC is charged up by HVCS internally at first and then by the auxiliary power supply.                                                                                                                                                                                                                                                                                                                                                  |

| 13, 18           | NC    | <b>Not connected.</b> NC is not connected in SOIC28 package and removed in TSSOP28 package to increase creepage distance.                                                                                                                                                                                                                                                                                                                                                            |

| 14               | HV    | <b>High-voltage current source for the IC start-up.</b> HV also acts as an X-cap discharger when the input voltage drops out.                                                                                                                                                                                                                                                                                                                                                        |

| 15               | BST   | <b>Voltage bootstrap.</b> BST is connected externally to a capacitor to build a power supply to drive the high-side MOSFET of the HB LLC.                                                                                                                                                                                                                                                                                                                                            |

| 16               | HSG   | <b>High-side gate driver of HB.</b> HSG is the gate driver output for the high-side MOSFET of the HB LLC.                                                                                                                                                                                                                                                                                                                                                                            |

| 17               | SW    | Reference of the high-side gate driver and bootstrap capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19               | HBVS  | Slope sensing to achieve adaptive dead-time adjustment. Detect the dv/dt of the half-bridge mid-point. A 5pF high-voltage capacitor is recommended between SW and HBVS. LLC works with fixed dead-time (about 300ns) when HBVS is floating. Connecting HBVS to GNDS disables the LLC switching.                                                                                                                                                                                      |

| 20               | GNDS  | Ground reference of LLC and power management circuits.                                                                                                                                                                                                                                                                                                                                                                                                                               |

# PIN FUNCTIONS (continued)

| Package<br>Pin # | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

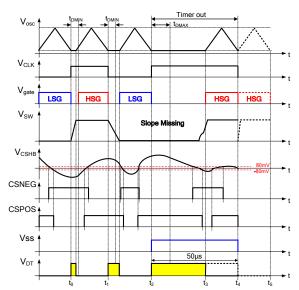

|                  |       | <ul> <li>Current sense of half-bridge. The LLC current can be sensed by a sense resistor or a capacitive divider.</li> <li>CSHB has the following functions: <ol> <li>Over-current regulation: As the voltage exceeds the V<sub>CS-OCR</sub> threshold, the soft-start capacitor on SS discharges internally. The frequency increases, limiting the output power. An output short circuit results in a nearly constant peak primary current. A timer set on ACIN limits the duration of this condition.</li> </ol> </li> </ul>                                                                                                                 |

| 21               | CSHB  | 2. Over-current protection: If the current continues to build up (despite the frequency increase) when the CSHB voltage reaches $V_{\text{CS-OCP}}$ , $C_{\text{SS}}$ is discharged continuously, and OCP is not triggered immediately until $V_{\text{SS}} < V_{\text{SS-OCP}}$ . If the condition for $V_{\text{CS}} > V_{\text{CS-OCP}}$ remains once $V_{\text{SS}}$ drops below $V_{\text{SS-OCP}}$ , the IC shuts down. $C_{\text{TIMER}}$ continues to be charged by an internal 140µA current source until the TIMER voltage reaches $V_{\text{th}2}$ . The IC resumes operation when the TIMER voltage falls below $V_{\text{th}3}$ . |

|                  |       | 3. Capacitive mode protection: The moment LSG is turned off, the CSHB voltage level is compared with a -80mV CMP threshold. If CSHB > -80mV, it blocks the HSG gate output until the slope comes down or the CMP timer runs out. Once HSG is turned off, CSHB is compared with a +80mV CMP threshold. If CSHB < +80mV, it blocks the LSG gate output until the slope comes up or the CMP timer runs out. As soon as capacitive mode is detected, the soft-start capacitor on SS discharges internally and the frequency increases.                                                                                                             |

|                  |       | All functions are disabled when CSHB is connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

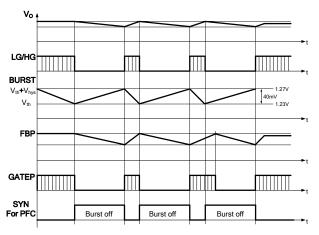

| 22               | BURST | <b>Burst mode control.</b> If the voltage on BURST is lower than $V_{th}$ (1.23V), the IC is disabled and resumes when the voltage exceeds 1.23V with a hysteresis of about 40mV. During burst mode, soft-start is not activated. This function helps reduce power loss at a lighter load.                                                                                                                                                                                                                                                                                                                                                     |

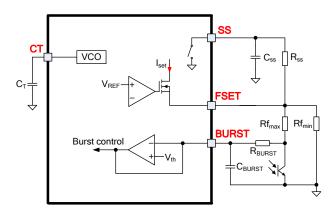

| 23               | FSET  | <b>Switching frequency set.</b> Provide a precise and stable V <sub>REF</sub> (1.97V) reference voltage. Current flowing out of FSET regulates the LLC switching frequency and output voltage. The minimum frequency is set via a resistor connected to GND. The resistor connecting the optocoupler and FSET sets the maximum frequency. An RC series connected from FSET to GND determines the specific operating frequency.                                                                                                                                                                                                                 |

| 24               | СТ    | <b>Time set.</b> Current flowing out of FSET is mirrored to charge and discharge the capacitor connected from CT to GNDS, which determines LLC switching frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 25               | SS    | <b>Soft-start for LLC.</b> Connect an external capacitor from SS to GND and a resistor to FSET to set both the maximum oscillator frequency and the time constant for the frequency shift during start-up. An internal switch discharges the capacitor when the chip is turned off to guarantee soft-start (all protections are listed except CMP).                                                                                                                                                                                                                                                                                            |

| 26               | V3.3  | A stable 3.3V voltage for digital PFC core or external circuit. A 10µF decoupling ceramic capacitor is recommended to connect V3.3 and GNDS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 27               | FBP   | Voltage sensing of PFC output. The voltage of FBP is sampled by ADC. FBP is also used in on-time calculation, OVP, OLP, and digital PI. A 3.3M $\Omega$ pull-down resistor is connected internally. It is recommended to connect a 680pF capacitor from FBP to GNDD.                                                                                                                                                                                                                                                                                                                                                                           |

| 28               | SCL   | I <sup>2</sup> C serial clock input. Connect a suitable pull-up resistor from SCL to V3.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

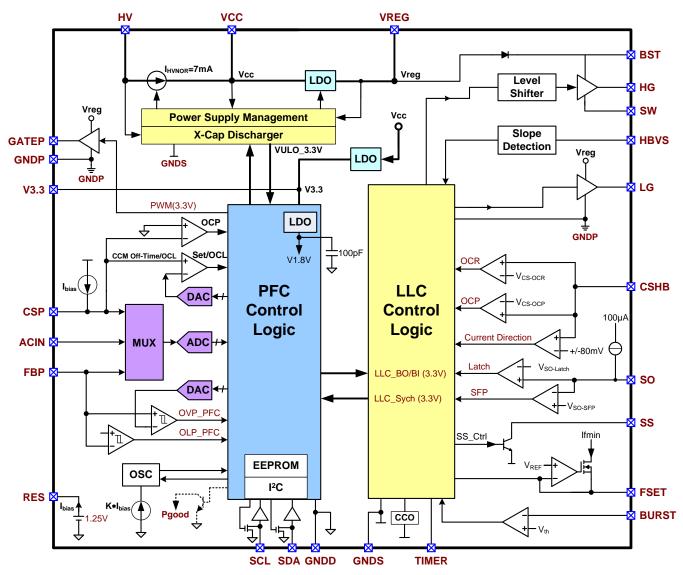

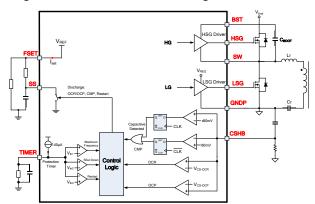

#### **BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

#### **FUNCTION DESCRIPTION**

The HR1200 is a high-performance combo controller that integrates digital PFC and HB LLC controllers.

#### **EEPROM**

The HR1200 applies EEPROM as the NVM. It has 1k bytes of data memory and 16 bytes of security memory.

There are only two commands used to operate the EEPROM:

- Read all the data from EEPROM to the memory map. This process operates automatically before the controller runs or receives a RESTORE\_USER\_ALL command (51h) from the I<sup>2</sup>C.

- Write all the data from the memory map to EEPROM. This process operates when it receives a STORE\_USER\_ALL command (50h) from the I2C.

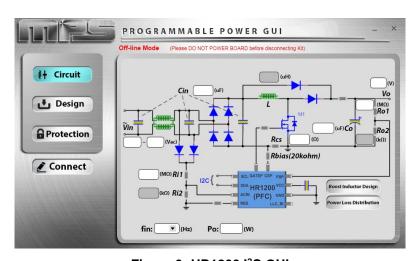

#### I<sup>2</sup>C Communication and GUI

The HR1200 has a standard I<sup>2</sup>C interface. It is recommended to select an I<sup>2</sup>C tool with 100kHz clock frequency. The I<sup>2</sup>C can read and write the memory map. It can also send a command to load the data from EEPROM to memory map or reload the data from memory map to EEPROM with the graphic user interface (GUI) (see Figure 3). For details, please refer to the "User Guideline\_HR1200 I<sup>2</sup>C Kit and GUI" and "User Guideline\_HR1200 Layout" files available on the MPS website.

#### **Power Supply Management**

This section describes how the HR1200 produces and optimizes the power supply for circuits inside the IC. Optimized power source can reduce no-load consumption and provide robust operation with sufficient fault protection. A high-voltage current source is also integrated in the IC for start-up and X-cap discharge when the AC input drops out.

#### **System Functions**

This section describes functions that HR1200 integrates to improve system performance, including X-cap discharge, IC on/off control, a power good signal, and an interface between the PFC stage and LLC stage for synchronous operation.

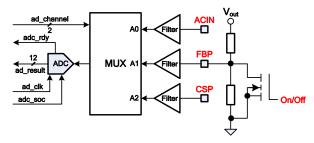

#### **Digital PFC Controller**

The HR1200 uses a digital PFC controller integrating digital logic, ADC, DAC, and comparators to achieve PFC functionality. To acquire programmable design parameters, I<sup>2</sup>C communication functions and EEPROM are also included.

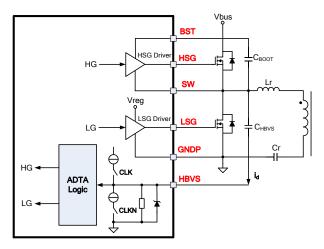

#### **HB LLC Controller**

The HB LLC converter can generate an isolated and regulated output voltage from the high voltage DC bus. With an adaptive dead-time control method, the HB LLC controller helps the converter operate in ZVS in a wider load range, improving the efficiency of the converter at light load. The IC implements anti-capacitive mode operation protection, allowing for robust product design.

Figure 3: HR1200 I<sup>2</sup>C GUI

© 2020 MPS. All Rights Reserved.

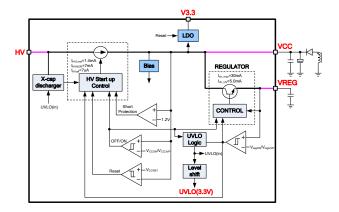

#### **Part 1: Power Supply Management**

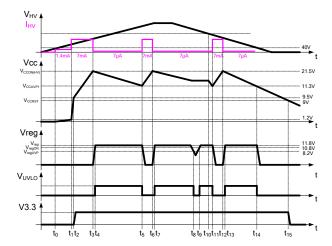

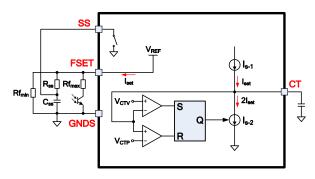

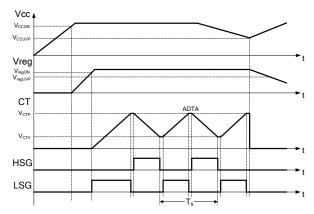

The power supply management function is implemented via four output pins: HV, VCC, VREG, and V3.3. Figure 4 and Figure 5 show the block diagram and operation waveforms of the power management circuit.

Figure 4: Block Diagram of Power Supply

Figure 5: Operation Waveforms of Power Supply

#### **High-Voltage Start-Up Input (HV)**

A 7mA current source charges VCC internally when a voltage larger than 40V is applied to HV. If VCC is lower than 1.2V, the charge current from HV is limited to  $I_{HVLimit}$  (1.4mA typically), to prevent excessive power loss caused by VCC short circuit during start-up.

During normal operation, the voltage on VCC rises quickly after start-up, and the HV current source switches to the nominal current  $I_{\text{HVNOR}}$  (7mA typically).  $I_{\text{HVNOR}}$  charges the capacitor connected to VCC externally, and VCC voltage ramps up. The HV current source is switched off when VCC voltage exceeds the start-up

level  $V_{\text{CCON(HV)}}$  (21.5V typically). The HV current source turns on again when VCC drops below  $V_{\text{CCUVP1}}$  (11.3V typically). Once the HV current source is turned off, the leakage current into HV should be below  $I_{\text{HVoff}}$  (7µA typically).

#### IC Supply Input (VCC)

VCC provides operational power for most of the internal circuits. Then the IC can start up with the HV start-up current source.

If the start-up current comes from HV when VCC reaches V<sub>CCON(HV)</sub>, the internal LDO is powered on. VREG begins building up, and the IC starts operating if no fault condition occurs. Then VCC is powered by the auxiliary winding of the HBC transformer. Once VCC drops below V<sub>CCUVP1</sub>, following actions occur:

- The IC stops operating, and the PFC controller stops switching immediately. But the HB LLC controller continues to operate until the low-side MOSFET becomes active.

- The VREG LDO is disabled.

The HV current source charges VCC until VCC reaches  $V_{CCON(HV)}$ , then VREG LDO is turned on again. If the IC enters latch mode, the latch status will remain until VCC falls below  $V_{CCRST}$ .

If VCC supplied by an external DC power source instead of HV current source, please refer to the HR1201 as an alternative.

#### Regulated Output (VREG)

An internal LDO is added to stabilize voltage in order to:

- Supply the internal PFC driver.

- Supply the internal low-side driver of HB LLC.

- Supply the internal high-side driver of HB LLC via a bootstrap diode.

- Supply a reference voltage.

The LDO is enabled only when VCC is higher than  $V_{\text{CCON(HV)}}$ . This ensures that any optional external circuitry connected to VREG does not dissipate any of the start-up current.

The IC starts switching only when VREG is higher than  $V_{regON}$  (10.8V typically). If VREG falls below  $V_{regUVP}$  (8.2V typically), the IC and the PFC controller stop switching immediately.

The HB LLC controller continues operating until the low-side MOSFET becomes active.

#### V3.3 for Digital Logic

V3.3 is a stabilized power supply for the internal digital logic. It is the output of an LDO with its input connected to VCC internally. The output of V3.3 is connected to a digital section with an internal bonding wire. When VCC is larger than V<sub>CCRST</sub> plus a hysteresis of about 0.5V, the V3.3 LDO is enabled. It can be disabled only when VCC is lower than  $V_{CCRST}$ .

The capacitor on V3.3 should be in the range of 4.7µF to 10µF to guarantee that V3.3 is stable.

Out from the 3.3V LDO, there is another LDO with 1.8V output downstream for powering the internal digital circuits.

#### UVLO (3.3V signal)

The UVLO (3.3V signal) is an enable signal for both the digital PFC and LLC controller. When VCC is larger than  $V_{CCUVP1}$ , and VREG is larger than  $V_{regON}$ , UVLO (3.3V signal) goes high.

#### **Part 2: System Functions**

#### X-Cap Discharger

X-caps are critical components placed at the input terminals of the power supply to filter out differential mode EMI noise. If the AC line voltage is removed, the redundant voltage on X-caps may cause harm to the user. Safety standards require the voltage to be discharged to a safe level within a certain time frame.

Commonly, resistors are placed in parallel with X-caps across the AC line to provide a discharge path. However, extra resistors bring continuous power consumption as long as the AC input is connected, which is the significant contributor to power consumption at no-load or standby conditions.

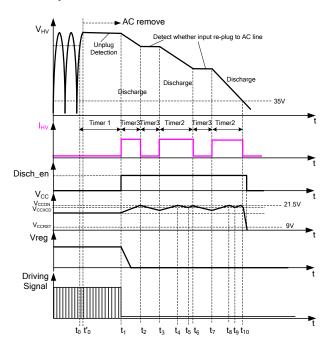

The HV current source in the HR1200 acts as a smart X-cap discharger when the AC input is removed. So, traditional discharge resistors can be eliminated. Operating waveforms are shown in Figure 6.

In a normal stage, the HV current source is off. The leakage current in HV is small, so power

consumption is reduced significantly. Once the AC voltage is disconnected, after a detection time window (Timer 1, 96ms typically), the IC controls the internal 7mA current source automatically to discharge energy from the X-cap to VCC within the Timer 3 period (48ms typically). The IC stops for an additional Timer 3 period to detect the AC. If no AC is re-applied during this last time period, the IC continues discharging during the Timer 2 period (144ms typically) until  $V_{HV}$  is below 35V. Once  $V_{HV}$  drops below 35V, VCC is discharged quickly by the internal current source, which speeds up recovery when the IC is in latch mode.

Figure 6: Operating Waveforms of X-Cap Discharger when AC Removed

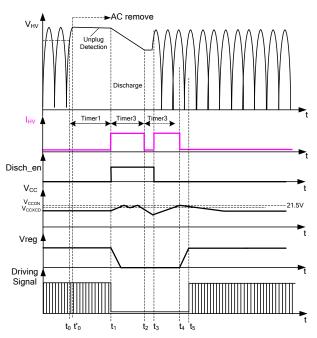

If the AC recovers in HV again during the Timer 3 period, a new start-up procedure begins (see Figure 7).

If the X-cap discharge function is enabled, VCC should be regulated between  $V_{\text{CCON}}$  and  $V_{\text{CCXCD}}$  to avoid over-stressing VCC.

The X-cap discharge function is very flexible, and allows users to choose an X-cap value to optimize differential mode EMI filtering without worrying about the effect of the required bleed resistors on the standby power budget and system no-load.

Figure 7: Operating Waveform of X-Cap Discharger when AC Recovered

#### **Over-Temperature Protection (OTP)**

Once the internal thermal sensor senses the IC temperature is over 145°C, the IC stops switching immediately. Both the LDO for VREG and V3.3 are disabled. If the IC temperature rises above 100°C, the high-voltage current source is disabled. The IC is enabled again when VCC drops below V<sub>CCRST</sub>. If the IC temperature drops below 100°C, the IC starts up again.

#### IC On/Off Control

The IC is turned off by pulling FBP down to GND with an external MOSFET (see Figure 8). If the FB voltage is less than 0.2V, both the PFC and LLC disable the PWM switching during startup or operation. When the FBP voltage is higher than 0.3V, the IC is turned on again. Besides, the IC can be turned off from the secondary side through an optocoupler.

Figure 8: IC On/Off Control

The IC can be disabled by programming the EEPROM through the I<sup>2</sup>C GUI (see Table 1).

Table 1: IC Disabled through I<sup>2</sup>C and MPS' GUI

| Resister<br>address |     | 56h |                 |                  |     |     |     |     |

|---------------------|-----|-----|-----------------|------------------|-----|-----|-----|-----|

| Bit                 | 7   | 6   | 5               | 4                | 3   | 2   | 1   | 0   |

| Access              | r/w | r/w | r/w             | r/w              | r/w | r/w | r/w | r/w |

| Function            |     |     | IC enable:      | LLC enable:      |     |     |     |     |

|                     |     |     | "1", enable IC  | "1", enable LLC  |     |     |     |     |

|                     |     |     | "0", disable IC | "0", disable LLC |     |     |     |     |

#### PFC and LLC Interface

There are two signals between the PFC and the LLC part:

#### 1. D2D brown-in/out signal (see Figure 9)

If the output voltage is higher than  $V_{D2D\_BI}$ , the D2D\_BI/BO signal is set high, enabling the LLC stage. The LLC stage is disabled when the output voltage drops below  $V_{D2D\_BO}$ . This function guarantees the LLC operates within a proper input voltage range, preventing the LLC from running in capacitive mode.

$V_{D2D\_BI}$  and  $V_{D2D\_BO}$  are programmable through  $I^2C$ . The register address for  $V_{D2D\_BI}$  is one word (16h, 17h). The register address for  $V_{D2D\_BO}$  is one word (18h, 19h). The value in the register can be calculated with Equation (1):

DEC2HEX

$$\left(V_{D2D\_BI/BO} \times 0.0032 \times \frac{1023}{1.6}\right)$$

(1)

#### 2. LLC burst synchronize signal

When the LLC operates in burst mode, the PFC burst mode can be synchronized with the LLC burst mode. This is achieved by setting bit 7 of register 56h high. When bit 7 is low, the LLC and PFC burst independently.

#### Part 3: PFC Controller

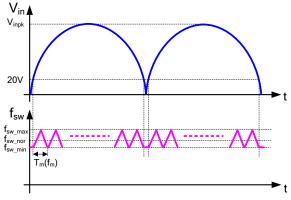

The state-of-the-art CCM/DCM control scheme can reduce the RMS current drawn from the AC mains by ensuring good shape of the input current both in CCM and DCM. The control scheme reduces the switching frequency when the load is reduced, therefore achieving higher efficiency and higher power factor at light load.

#### **Digital PFC Timing**

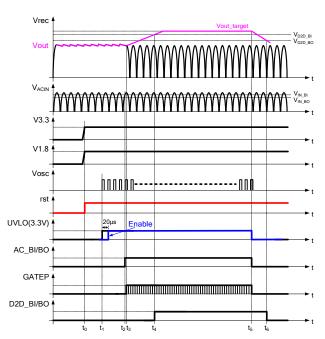

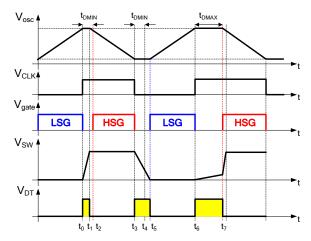

Figure 9 shows the timing of the digital PFC block.

Figure 9: Power Supply Sequence of Digital Controller

#### Timing of the Power Supply

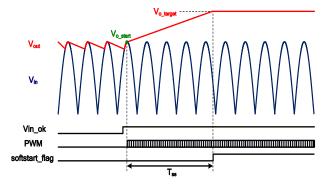

Once VCC rises above  $V_{\text{CCRST}}$  plus a hysteresis of about 0.5V, the V3.3 LDO is enabled and an internal LDO downstream produces a stable 1.8V power supply for the internal digital logic and system clocks. The rst signal is set high when both 3.3V and 1.8V are stable. When UVLO (3.3V signal) is validated, the IC enables OSC, ADC, DAC, and relative comparators. The enable signal is set high after a delay of 20µs, which indicates the digital core is ready to begin operation.

#### Timing of the Digital Core

If the enable signal is high, ADC begins sampling  $V_{ACIN}$  and  $V_{FBP}$ . If the AC input meets the brown-in condition and no open-loop fault is found on FBP, the AC\_BI/BO signal is set high. The PFC soft starts until the output reaches the target value. While the PFC output voltage ramps up above  $V_{D2D-BI}$ , D2D\_BI/BO is set high. the downstream LLC starts operating.

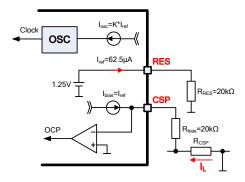

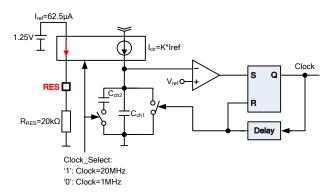

#### **Reference Current (RES)**

RES is connected internally to a precise reference voltage of 1.25V (see Figure 10). RES should be connected to a  $20k\Omega$ , 0.5% resistor externally. Reference current about 62.5 $\mu$ A is then generated. The current is

mirrored and flows out of CSP. If CSP is also connected externally to a  $20k\Omega$  resistor, a bias voltage of 1.25V on CSP is produced, which keeps the CSP voltage positive (see Figure 11).

Figure 10: Reference Current

Moreover, the reference current is mirrored to produce a system clock (see Figure 11).

Figure 11: System Clock Generator

The system clock switches from 20MHz to 1MHz when PWM is disabled (i.e. burst off, OVP, OCP, etc.) in order to reduce IC power consumption.

#### Input Voltage Sensing

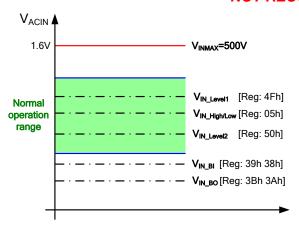

The input voltage is rectified and attenuated by a resistor divider with a fixed ratio (0.0032) before provided to the ACIN input. Then, the ADC samples the voltage on ACIN including the instantaneous value, the peak value, and the frequency of the input voltage. The data are used for on-time calculation, AC brown-in/out protection, capacitor current compensation and X-cap discharge.

Figure 12 shows the input voltage level defined for different functions. All parameters can be programmed through the I<sup>2</sup>C Kit and MPS' GUI.

Figure 12: Input Voltage Level for Different Functions

#### Input Brown-In/Brown-Out

If  $V_{ACIN}$  is larger than the brown-in threshold  $(V_{IN\_BI})$ , it means the IC is ready to switch. If  $V_{ACIN}$  is less than the brown-out threshold  $(V_{IN\_BO})$  for the length of one timer period, the IC stops switching.  $V_{IN\_BI}$  and  $V_{IN\_BO}$  are 10-bit values that are stored in the registers from 38h to 38h. The values can be calculated with Equation (2):

DEC2HEX

$$\left(V_{IN\_BI/BO} \times 0.0032 \times \frac{1023}{1.6}\right)$$

(2)

The brown-in and brown-out timer is set in register 3Ch (see Table 2).

Table 2: Brown-In/Out Timer in Register 3Ch

| Bit | Item        | Description    |

|-----|-------------|----------------|

| 7:4 | VIN_BI_TIME | Brown-in time  |

| 3:0 | VIN_BO_TIME | Brown-out time |

#### **High/Low Line**

The low line is determined when the input voltage is lower than  $V_{\text{IN\_High/Low}}$ . The high line is determined when the input voltage is larger than  $V_{\text{IN\_High/Low}}$  plus a hysteresis of about 10V. The high/low-line signal sets the soft-start time and the resonant time for valley turn-on. It also regulates the output voltage at different levels to optimize the efficiency of the PFC stage.

V<sub>IN\_Level1</sub>, V<sub>IN\_High/Low</sub> and V<sub>IN\_Level2</sub> separate the input voltage into four ranges to achieve different compensation values to improve PF at different input voltage ranges.

The thresholds are 8-bit data. The value can be set according to Equation (3):

DEC2HEX

$$\left(V_{\text{IN\_High/Low}} \times 0.0032 \times \frac{256}{1.6}\right)$$

(3)

#### **Output Voltage Sensing**

Similar to input voltage sensing, the output voltage is attenuated by a resistor divider before connected to FBP. Then the voltage on FBP is sampled by ADC. The results are used for on-time calculation and a series of protections.

The internal pull down resistor of  $3.3M\Omega$  should be considered when designing the external resistors. Make the total divided ratio to 0.0032 according to Equation (4):

$$\frac{R_{FBL-L} // 3.3M\Omega}{R_{FBL-H} + (R_{FBL-L} // 3.3M\Omega)} = 0.0032$$

(4)

Where RFBL-H is the divider resistor connected on high-side and RFBL-L is the divider resistor connect on low-side.

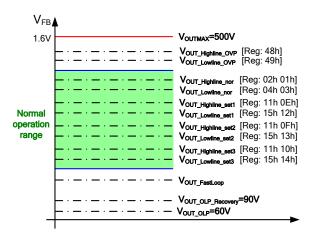

Figure 13 shows the output voltage level that is defined for different functions. All parameters can be programmed through the I<sup>2</sup>C GUI.

Figure 13: Output Voltage Level for Different Functions

#### **Output Regulation**

To optimize efficiency, the output voltage can be auto-regulated according to the input voltage and output power. The output voltage is divided into two ranges by  $V_{\text{IN\_High/Low}}$  and is divided into four ranges according to the output power level, which can be programmed by registers from 06h to 0Bh. Therefore, the IC can auto-regulate eight output voltages accordingly.

#### **Output Fast OVP**

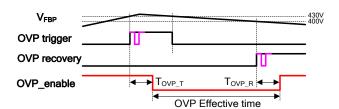

$V_{\text{OUT\_Highline\_OVP}}$  and  $V_{\text{OUT\_Lowline\_OVP}}$  are 7-bit values stored in register 48h and 49h. They are programmable through the I²C GUI (430V typically). A 7-bit DAC converts  $V_{\text{OUT\_OVP}}$  to an analog signal and compares the result with FBP voltage. If output voltage is larger than  $V_{\text{OUT\_OVP}}$ , the PFC stops switching. Once output voltage decreases to regulation voltage, the PFC resumes switching. Figure 14 shows the OVP circuit.

Figure 14: OVP Circuit

A blanking time is inserted in OVP, keeping the IC immune to switching noise interference (see Figure 15). Both of  $T_{\text{OVP\_T}}$  and  $T_{\text{OVP\_R}}$  are programmable in register 60h.

Figure 15: Output Fast OVP

#### **Fast Loop**

In a dynamic load event, the PFC output voltage decreases due to the low bandwidth of the voltage control loop, which may cause the output voltage to fall out of the regulated range. Fast loop is activated when the output voltage is lower than V<sub>OUT\_FastLoop</sub>. Then Ki and Kp of the digital PI are changed with X times the normal value, depending on the GUI setting. In this way, the output voltage of the PFC is regulated faster in the dynamic load event.

#### Open Loop or IC Disable Condition

If the FBP voltage is less then  $V_{OUT\_OLP}$  (60V typically), it is considered to be an open-loop or IC disable condition. The IC does not work and PWM switching is disabled during operation. The IC restarts only when the FBP voltage is larger than  $V_{OUT\_OLP\_Recovery}$  (90V typically). The

open loop is achieved by software and the value is fixed.

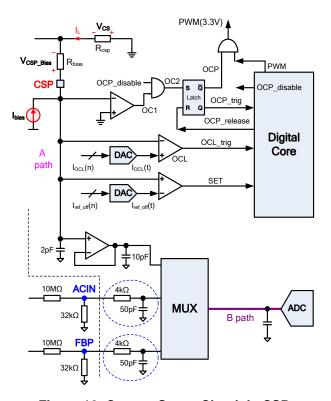

#### **Peak Current Sensing**

The PFC inductor current is sensed by  $R_{\text{CSP}}$  and produces a negative voltage. A precise current source ( $I_{\text{bias}}$ ) exits CSP and produces a positive bias voltage on  $R_{\text{bias}}$  (see Figure 16).

The CSP voltage is calculated with Equation (5):

$$V_{CSP}(t) = V_{CSP\_Bias}(t) - V_{CS}(t)$$

(5)

Figure 16: Current Sense Circuit in CSP

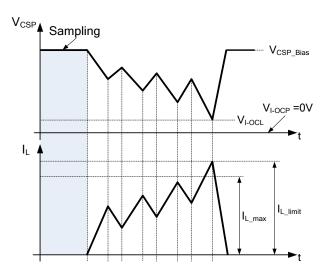

Overall, the CSP voltage is positive (see Figure 17). The ADC samples  $V_{\text{CSP\_Bias}}$  (1.25V typically) regularly.

Figure 17: Voltage Waveform in CSP

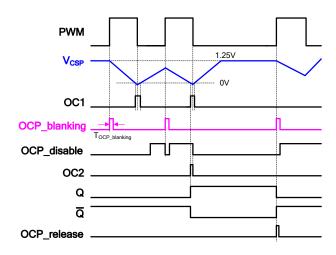

#### **Over-Current Protection (OCP)**

If the CSP voltage is less than zero, overcurrent protection is enabled. The PFC stops switching immediately, and OCP\_trig is set high simultaneously. The digital core detects this status and disables the PWM. OCP can be released by the OCP\_release signal.

The OCP function is disabled by setting bit 3 of register 45h to logic low. The OCP behavior mode can be programmed by setting bit 2 to bit 0 of register 45h. It can be hiccup, latch or autorestart with a delay time. The default setting is hiccup. The delay time is set in register 46h.

A programmable LEB1 (T<sub>OCP\_blanking</sub>) of about 200ns is implemented to avoid error sensing due to switching noise.

The OCP function can avoid over-stressing when the inductor is shorted, or when the current is too large.

Figure 18 shows the operating waveforms of the OCP function.

Figure 18: OCP Operation Waveform

#### **Over-Current Limit (OCL)**

The inductor current exists a cycle-by-cycle limit by setting the appropriate  $R_{CSP}$  and  $V_{I\text{-}OCL}$ .  $V_{I\text{-}OCL}$  can be programmed in register 44h, and it can be converted to an analog signal by a 7-bit DAC. A programmable LEB1 ( $T_{OCL\_blanking}$ ) of about 200ns is inserted to avoid switching noise if the digital core is turned on (similar to  $T_{OCP\_blanking}$ ).

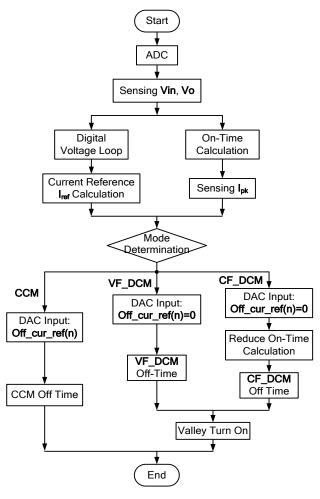

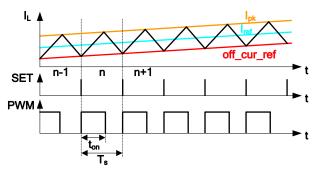

#### **Digital PFC Control Scheme**

Figure 19 shows the flowchart of the digital PFC control scheme.

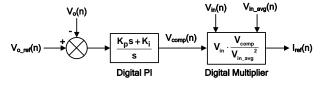

#### Digital Current Reference

The digital PI compensates for the voltage loop. Its output  $V_{comp}(n)$  is sent to the multiplier for current reference calculation (see Figure 20).

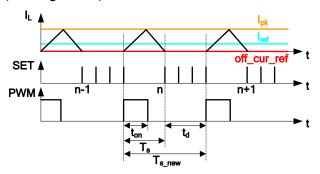

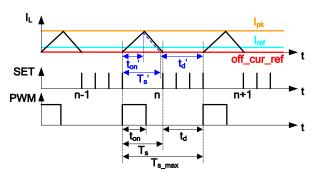

Figure 19: Flowchart of PFC Control Scheme