# MP5461

# Dual Input, 4-Switch Integrated Buck-Boost Converter with Input ORing and Selection

#### DESCRIPTION

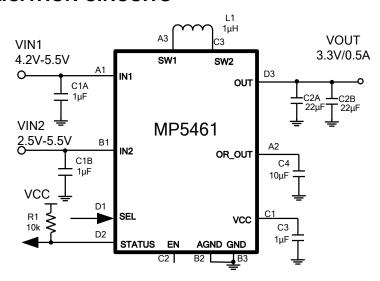

The MP5461 is a dual input, 4-switch, integrated buck-boost converter. It is capable of regulating the output voltage from 4.2V to 5.5V VIN1 and 2.5V to 5.5V VIN2. The VIN1 can support up to 22V input voltage but is not functional after >5.75V.

The MP5461 has two auto-ORing switches from VIN1 and VIN2 to achieve a stable input for the buck-boost converter. The two sets of ORing MOSFETs are integrated. If one channel power source falls, the fast turn-off protection minimizes the reverse current.

The buck-boost converter can operate from an input voltage above, equal to, or below the output voltage. It uses current-mode control with 1.8MHz fixed PWM frequency to optimize stability and transient response. In a light-load condition, it enters PFM mode to get high light-load efficiency. Integrated MOSFETs minimize the solution size while maintaining high efficiency.

Fault protection includes VIN1 OVP shutdown, output hiccup current limiting, and thermal shutdown.

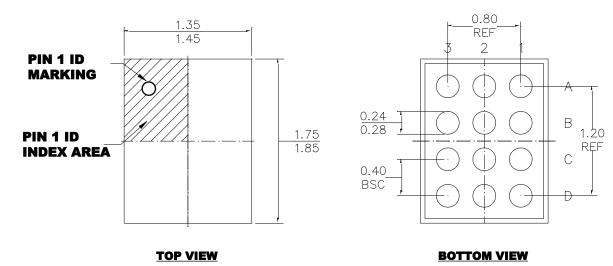

The MP5461 is available in a tiny CSP-12 (1.4mmx1.8mm) package.

#### **FEATURES**

- Dual Input ORing Switches:

- 4.2V to 5.5V Input Voltage Range for VIN1

- Supports 22V Voltage Stress for VIN1

- 5.75V OVP Shutdown for VIN1

- 2.5V to 5.5V Input Voltage Range for VIN2

- Fast Reverse Block within 2µs

- 1A Current Capability for Each Channel

- Soft-Start Control

- Fast SCP (Short-Circuit Protection) on OR OUT

- Power-Path Selection Input

- Power-Path Status Indication

- Buck-Boost Converter

- 1.8MHz Switching Frequency for CCM

- 3.3V Fixed Output Voltage

- 500mA Continuous Output Current

- 1ms Soft-Start Time

- o Auto PFM/PWM Mode

- Output Over-Voltage Protection

- Hiccup Over-Current Protection

- 1µA Shutdown Current

- 200µA Quiescent Current

- Active Low System EN Pin

- EN to OR OUT Start-Up Delay 300µs

- Over-Temperature Shutdown

- Available in a Wafer Level Chip Scale Packaging: CSP-12(1.4mmx1.8mm)

#### **APPLICATIONS**

- USB-C Cable

- V<sub>CONN</sub> Powered USB Device

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

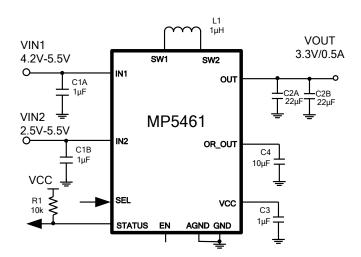

# **TYPICAL APPLICATION**

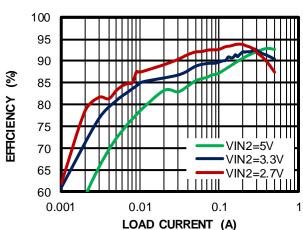

# Efficiency vs. Load Current

#### **ORDERING INFORMATION**

| Part Number* | Package              | Top Marking |  |

|--------------|----------------------|-------------|--|

| MP5461GC     | CSP-12 (1.4mmx1.8mm) | See Below   |  |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP5461GC-Z).

# **TOP MARKING**

JGY

LLL

JG: Product code of MP5461GC

Y: Year code LLL: Lot number

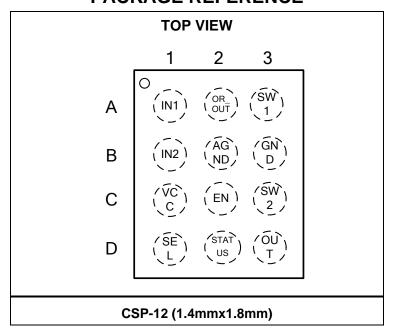

#### **PACKAGE REFERENCE**

© 2019 MPS. All Rights Reserved.

#### **PIN FUNCTIONS**

| CSP-12<br>Pin # | Name   | Description                                                                                                                                                                                                                                                    |  |  |  |

|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1              | IN1    | <b>VIN1 supply voltage.</b> The MP5461 operates from a 4.2V to 5.5V VIN1 voltage and supports a 22V input voltage, but it is not functional >5.75V. CIN1 preven large voltage spikes at the input. Place CIN1 as close to the IC as possible.                  |  |  |  |

| A2              | OR_OUT | <b>IN1, IN2 ORing output.</b> Also functions as the buck-boost input pin. Use a 10μF or larger capacitor for decoupling.                                                                                                                                       |  |  |  |

| А3              | SW1    | <b>Switch1.</b> The first half-bridge switch node is connected to SW1. Connect an inductor between SW1 and SW2.                                                                                                                                                |  |  |  |

| B1              | IN2    | <b>VIN2 supply voltage.</b> The MP5461 operates from a 2.5V to 5.5V VIN2 voltage. CIN2 prevents large voltage spikes at the input. Place CIN2 as close to the IC as possible.                                                                                  |  |  |  |

| B2              | AGND   | <b>Analog ground.</b> Connect AGND to VCC capacitor's GND node by a Kelvin sense trace.                                                                                                                                                                        |  |  |  |

| В3              | GND    | <b>Power ground.</b> Reference ground of the regulated output voltage. GN requires extra care during PCB layout. Connect to GND with copper traces are vias.                                                                                                   |  |  |  |

| C1              | VCC    | Internal 5V LDO regulator output. Decouple with a 1µF capacitor.                                                                                                                                                                                               |  |  |  |

| C2              | EN     | <b>On/off control for entire chip.</b> EN is active low. Drive EN high to turn off the chip. Drive EN low or float to turn on the device. It has an internal $600k\Omega$ pull-down resistor to ground.                                                        |  |  |  |

| C3              | SW2    | <b>Switch2.</b> The internal second half-bridge switch node is connected to SW2. Connect an inductor between SW1 and SW2.                                                                                                                                      |  |  |  |

| D1              | SEL    | <b>Power path select input.</b> If SEL=Low or is floated, VIN1 is selected; If SEL=High, VIN2 is selected. The MP5461 will auto select the available power path if only one supply is available. It has an internal $600k\Omega$ pull-down resistor to ground. |  |  |  |

| D2              | STATUS | <b>Status indication.</b> Open drain output. Indicates if the VIN1 or VIN2 channel is selected. Refer to the truth table.                                                                                                                                      |  |  |  |

| D3              | OUT    | Output pin.                                                                                                                                                                                                                                                    |  |  |  |

| ABSOLUTE MAXIMUM RATINGS (1) Supply Voltage (V <sub>IN1</sub> )0.3V to +24V                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{\text{SW1}}$                                                                                                                                  |

| $V_{\text{SW2}}$                                                                                                                                  |

| $V_{\text{EN}}, V_{\text{SEL}}, V_{\text{STATUS}}$                                                                                                |

| Junction Temperature                                                                                                                              |

| Recommended Operating Conditions (3)                                                                                                              |

| Operation Input Voltage VIN14.2V to 5.5V Operation Input Voltage VIN22.5V to 5.5V Output Current500mA Operating Junction Temp. (TJ)40°C to +125°C |

**Thermal Resistance** (4) **θ**<sub>JA</sub> **θ**<sub>JC</sub> CSP-12 (1.4mmx1.8mm) ...... 110 ..... 12... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB. The value of θJA given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7 and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN1}$  = 5V,  $V_{IN2}$ =5V,  $V_{EN}$  = 0V,  $T_J$  = -40°C to +125°C<sup>(5)</sup>, unless otherwise noted.

| Parameter                                                   | Symbol               | Condition                                                                    | Min  | Тур  | Max  | Units |

|-------------------------------------------------------------|----------------------|------------------------------------------------------------------------------|------|------|------|-------|

| Supply current (Shutdown)                                   | I <sub>IN1</sub>     | $V_{EN}$ =5V, VIN1=5V, VIN2=float, $T_J$ = +25°C                             |      | 1    | 5    | μA    |

| Supply current (Shutdown)                                   | I <sub>IN2</sub>     | V <sub>EN</sub> =5V, VIN1=float, VIN2=5V,<br>T <sub>J</sub> = +25°C          |      | 1    | 5    | μA    |

| Supply ourrent (Quiescent)                                  | I <sub>Q1</sub>      | $V_{EN}=0V$ , VIN1=5V, VIN2=float, No switching, $T_J=-40^{\circ}C$ to +85°C |      | 210  | 260  | μA    |

| Supply current (Quiescent)                                  | I <sub>Q2</sub>      | $V_{EN}=0V$ , VIN1=float, VIN2=5V, No switching, $T_J=-40^{\circ}C$ to +85°C |      | 185  | 230  | μA    |

| EN logic high input                                         | $V_{EN\_H}$          | Disable Part                                                                 | 1.2  |      |      | V     |

| EN logic low input                                          | V <sub>EN_L</sub>    | Enable Part                                                                  |      |      | 0.4  | V     |

| EN to ground resistance                                     | Ren                  |                                                                              |      | 600  |      | kΩ    |

| Thermal shutdown <sup>(6)</sup>                             | T <sub>STD</sub>     |                                                                              |      | 150  |      | °C    |

| Thermal hysteresis <sup>(6)</sup>                           | T <sub>HYS</sub>     |                                                                              |      | 20   |      | °C    |

| VCC regulator                                               | Vcc                  | VIN1=5.5V                                                                    | 4.5  | 5    | 5.5  | V     |

| VCC load regulation                                         | Vcc_rg               | Icc=0-5mA                                                                    |      | 3    | 5    | %     |

| Dual Input ORing Switches                                   |                      |                                                                              |      | l    | l    | J     |

| V <sub>IN1</sub> under-voltage lockout threshold rising     | IN1UV <sub>Vth</sub> |                                                                              | 3.6  | 3.9  | 4.15 | V     |

| V <sub>IN1</sub> under-voltage lockout threshold hysteresis | IN1UV <sub>HYS</sub> |                                                                              |      | 400  |      | mV    |

| V <sub>IN2</sub> under-voltage lockout threshold rising     | IN2UV <sub>Vth</sub> |                                                                              | 2.05 | 2.25 | 2.45 | V     |

| V <sub>IN2</sub> under-voltage lockout threshold hysteresis | IN2UV <sub>HYS</sub> |                                                                              |      | 150  |      | mV    |

| EN to OR_OUT startup                                        | t <sub>EN_DLY1</sub> | EN=0 to OR_OUT>90%, IN1=5V, IN2=0                                            |      | 300  |      | μs    |

| delay                                                       | ten_DLY2             | IN2=5V, IN1=0                                                                |      | 300  |      | μs    |

| Input over-voltage rising                                   | $V_{\text{OVP\_R}}$  | IN1 only                                                                     | 5.51 | 5.75 | 6.1  | V     |

| OVP recovery threshold                                      | $V_{OVP_F}$          | IN1 only                                                                     |      | 5.5  |      | V     |

| Switch1 on resistance                                       | R <sub>DSON1</sub>   | VCC=5V                                                                       |      | 160  |      | mΩ    |

| Switch2 on resistance                                       | R <sub>DSON2</sub>   | VCC=5V                                                                       |      | 90   |      | mΩ    |

| IN1 to OR_OUT regulation voltage                            | $V_{REG1}$           | lo=1mA, lo=100mA                                                             | 5    | 40   | 100  | mV    |

| IN2 to OR_OUT regulation voltage                            | V <sub>REG2</sub>    | lo=1mA, lo=100mA                                                             | 5    | 40   | 100  | mV    |

| Reverse voltage turn-off response time <sup>(7)</sup>       | t <sub>RV</sub>      |                                                                              |      | 2    |      | μs    |

| SEL logic high input                                        | V <sub>SEL_H</sub>   | VIN2 is selected                                                             | 1.2  |      |      | V     |

| SEL logic low input                                         | V <sub>SEL_L</sub>   | VIN1 is selected                                                             |      |      | 0.4  | V     |

| SEL to ground resistance                                    | Rsel                 |                                                                              |      | 600  |      | kΩ    |

| STATUS pin leakage                                          | I <sub>STA_LKG</sub> | Pull-up with 5V                                                              |      |      | 1    | μΑ    |

| STATUS low voltage                                          | V <sub>STA_Low</sub> | Sink 1mA                                                                     |      |      | 50   | mV    |

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN1}$  = 5V,  $V_{IN2}$ =5V,  $V_{EN}$  = 0V,  $T_J$  = -40°C to +125°C<sup>(5)</sup>, unless otherwise noted.

| Parameter                               | Symbol                   | Condition                 | Min   | Тур  | Max   | Units            |

|-----------------------------------------|--------------------------|---------------------------|-------|------|-------|------------------|

| STATUS delay                            | T <sub>STA_DEG</sub>     | Rising edge               |       | 25   |       | μs               |

|                                         |                          | Falling edge              |       | 55   |       |                  |

| Buck-Boost                              |                          |                           |       |      |       |                  |

| Output voltage                          | Vouт                     |                           | -1.5% | 3.3  | +1.5% | V                |

| Output over-voltage protection          | Vout_ovp_r               |                           | 110%  | 115% | 120%  | Vоит             |

| Output OVP recovery                     | $V_{\text{OUT\_OVP\_F}}$ |                           |       | 105% |       | V <sub>OUT</sub> |

| OVP discharge resistance                | R <sub>DIS</sub>         |                           |       | 1    |       | kΩ               |

| Oscillator frequency                    | Fs                       |                           | 1.45  | 1.8  | 2.15  | MHz              |

| Steady state current limit              | I <sub>LIM</sub>         | VOUT=0V                   | 1.65  | 2.5  | 3.35  | Α                |

| SWD valley current limit <sup>(7)</sup> |                          |                           |       | -1.5 |       | Α                |

| PMOS on resistance                      | R <sub>DS(on)-P</sub>    | SWA, SWD, 3.3Vin, 3.3Vout |       | 90   |       | mΩ               |

| NMOS on resistance                      | R <sub>DS(on)-N</sub>    | SWB, SWC, 3.3Vin, 3.3Vout |       | 80   |       | mΩ               |

| Soft-start time                         | Tss                      | 0-100%Vout                |       | 1    |       | ms               |

#### NOTE:

- 5) All min/max parameters are tested at T<sub>J</sub>=25°C. Limits over temperature are guaranteed by design, characterization and correlation.

- 6) Guaranteed by design.

- 7) Guaranteed by engineering sample characterization.

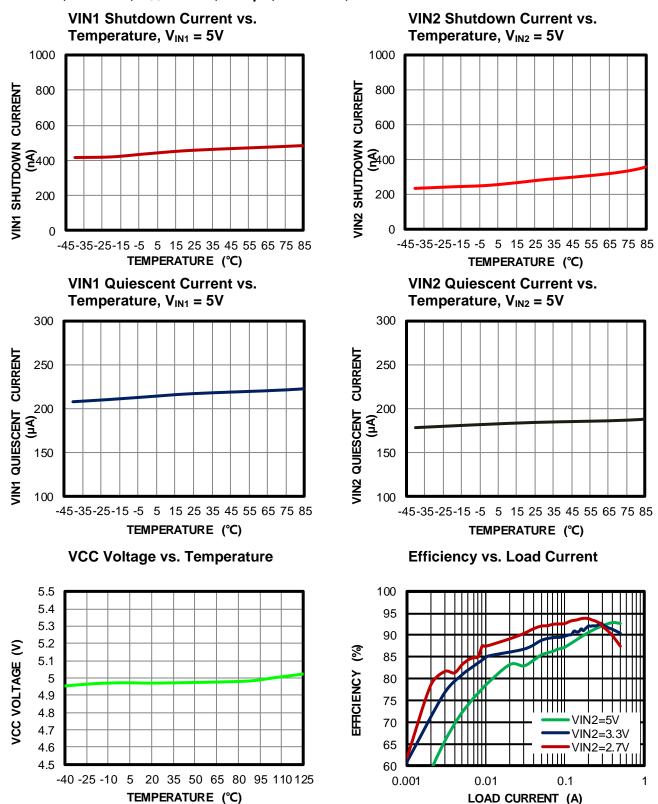

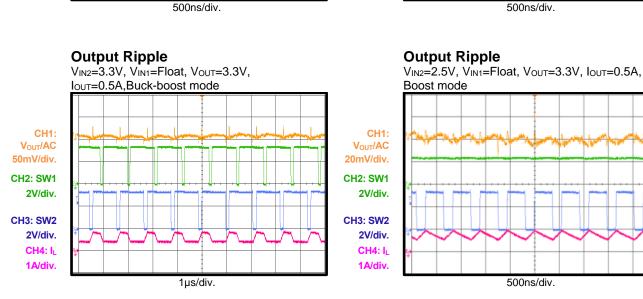

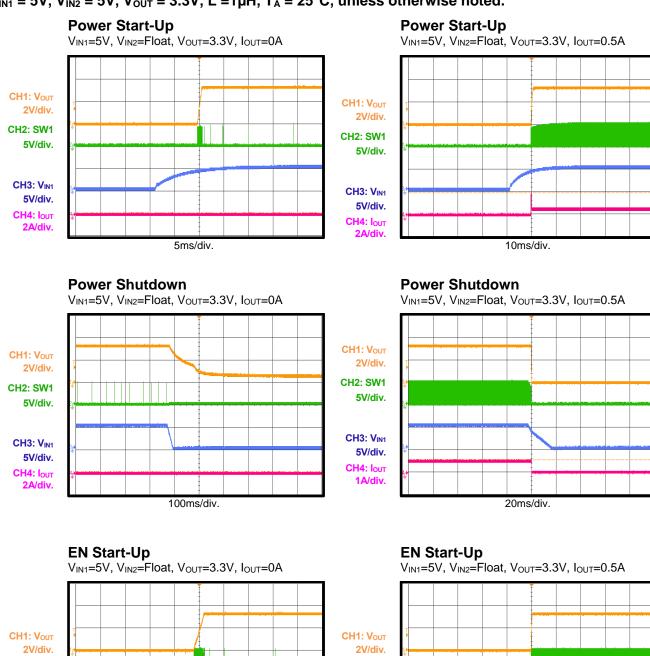

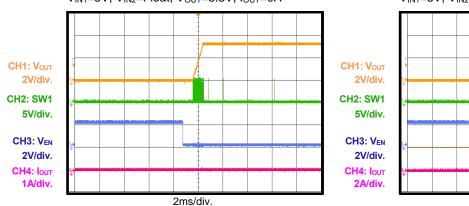

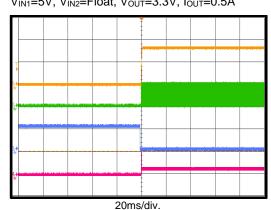

#### TYPICAL PERFORMANCE CHARACTERISTICS

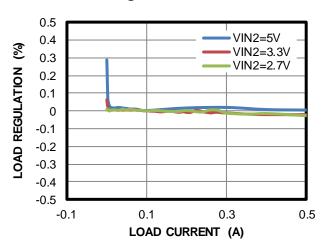

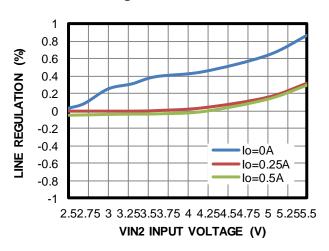

$V_{IN1} = 5V$ ,  $V_{IN2} = 5V$ ,  $V_{OUT} = 3.3V$ , L =1 $\mu$ H,  $T_A = 25$ °C, unless otherwise noted.

$V_{\text{IN1}}$  = 5V,  $V_{\text{IN2}}$  = 5V,  $V_{\text{OUT}}$  = 3.3V, L =1 $\mu$ H,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

#### **Load Regulation**

#### **Line Regulation**

© 2019 MPS. All Rights Reserved.

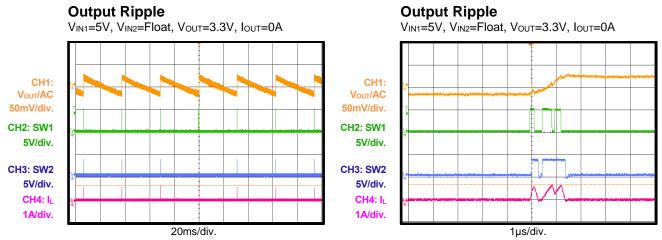

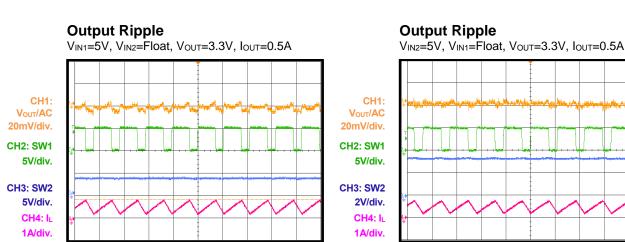

$V_{IN1} = 5V$ ,  $V_{IN2} = 5V$ ,  $V_{OUT} = 3.3V$ , L =1 $\mu$ H,  $T_A = 25$ °C, unless otherwise noted.

$V_{IN1} = 5V$ ,  $V_{IN2} = 5V$ ,  $V_{OUT} = 3.3V$ , L =1 $\mu$ H,  $T_A = 25$ °C, unless otherwise noted.

$V_{IN1} = 5V$ ,  $V_{IN2} = 5V$ ,  $V_{OUT} = 3.3V$ , L =1 $\mu$ H,  $T_A = 25$ °C, unless otherwise noted.

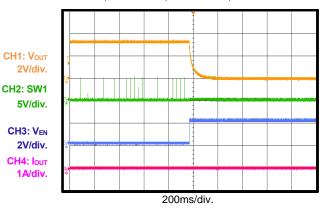

V<sub>IN1</sub>=5V, V<sub>IN2</sub>=Float, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=0A

#### **EN Shutdown**

CH1: Vout

CH2: SW1

2V/div.

5V/div.

CH3: VEN

CH4: lout

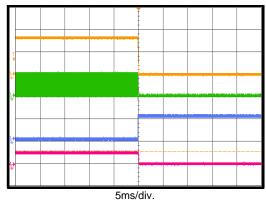

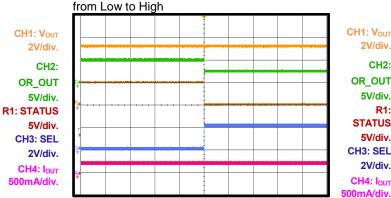

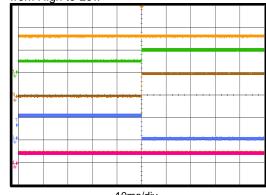

CH1: V<sub>OUT</sub>

2V/div.

OR OUT

5V/div.

5V/div.

2V/div.

CH3: SEL

CH4: I<sub>OUT</sub>

CH1: Vout

CH2: SW1

CH3: SW2 5V/div.

CH4: IL

2A/div.

2V/div.

5V/div.

R1: **STATUS**

CH2:

1A/div.

2V/div.

V<sub>IN1</sub>=5V, V<sub>IN2</sub>=Float, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=0.5A

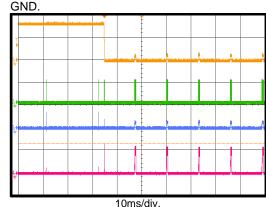

#### Input Voltage Selection by SEL Pin

VIN1=5V, VIN2=2.5V, VOUT=3.3V, IOUT=0.2A, SEL

# Input Voltage Selection by SEL Pin

VIN1=5V, VIN2=2.5V, VOUT=3.3V, IOUT=0.2A, SEL

from High to Low

10ms/div.

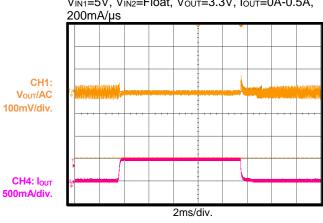

#### **Load Transient**

V<sub>IN1</sub>=5V, V<sub>IN2</sub>=Float, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=0A-0.5A,

2ms/div.

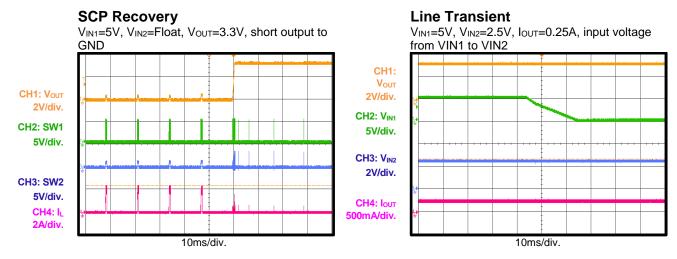

# **SCP Entry**

V<sub>IN1</sub>=5V, V<sub>IN2</sub>=Float, V<sub>OUT</sub>=3.3V, short output to

$V_{\text{IN1}}$  = 5V,  $V_{\text{IN2}}$  = 5V,  $V_{\text{OUT}}$  = 3.3V, L =1 $\mu$ H,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

© 2019 MPS. All Rights Reserved.

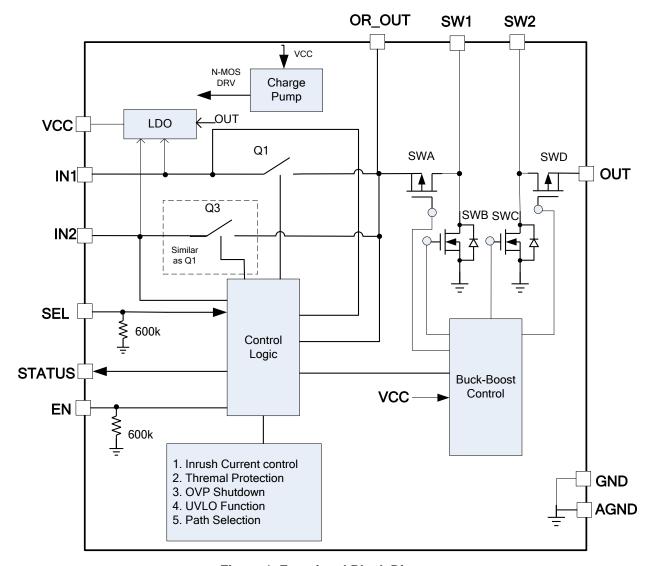

# **BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

Table 1: Truth Table of SEL and STATUS Logic

| Table 1. Trust Table of SEE and STATOS Edgic |                     |                             |                          |                 |                                                   |  |

|----------------------------------------------|---------------------|-----------------------------|--------------------------|-----------------|---------------------------------------------------|--|

| VIN1 VIN2                                    | VIN2                | SEL Input                   | Power path               | ORing<br>Output | STATUS                                            |  |

|                                              |                     | (SEL="low or float" selects |                          | Output          | (Open drain output.                               |  |

|                                              |                     | VIN1 SEL="high"             |                          |                 | Open drain: VIN1 is<br>selected; or VIN1/2<br>N/A |  |

|                                              |                     | selects VIN2)               |                          |                 | Low: VIN2 is selected)                            |  |

| 4.2V-5.5V 2.5V-5.5V                          | 0.5/.5.5/.          | "0", Select<br>VIN1         | VIN1 —O OUT              | OUT=VIN1        | Open drain                                        |  |

|                                              | 2.5V-5.5V           | "1", Select<br>VIN2         | VIN1 — OUT<br>VIN2 — OUT | OUT=VIN2        | 0                                                 |  |

| Not 4.2V-5.5V available or <2.5V             | "0", Select<br>VIN1 | VIN1 — OUT VIN2 — OUT       | OUT=VIN1                 | Open drain      |                                                   |  |

|                                              | "1", Select<br>VIN2 |                             |                          | Open drain      |                                                   |  |

| Not available<br>or <4.2V<br>or >5.75V       | 2.5V-5.5V           | "0", Select<br>VIN1         | VIN1 — O——OUT VIN2 —     | OUT=VIN2        | 0                                                 |  |

|                                              |                     | "1", Select<br>VIN2         | VIN2 — O O               |                 | 0                                                 |  |

|                                              | Not<br>available or | "0", Select<br>VIN1         | VIN1 —o — OUT            | OUT=0           |                                                   |  |

|                                              | <2.5V               |                             | VIN2 — o o               |                 | Open drain                                        |  |

#### **OPERATION**

The MP5461 is a dual input, high-efficiency, buckboost converter that provides regulated output voltage above, equal to, or below the input voltage.

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) is used to protect the device from operating at an insufficient supply voltage. The MP5461 UVLO circuit monitors the IN1 and IN2 voltage. During start-up, either IN1 or IN2 must rise higher than V<sub>IN-UVLO</sub> to enable the IC.

#### **EN**

EN is the system on/off control input. It's an active low input. EN has an internal weak pull-down resistor. Pull EN low or float to enable the MP5461. Pull EN high to disable the MP5461.

#### **VCC Power Supply**

When EN is active, IN1 and IN2 charges the VCC. IN1 is a high voltage pin; there is a LDO from IN1 to VCC. An ORing block will determine using the IN1 LDO output or IN2 to supply VCC. All internal circuits of the MP5461 are supplied by VCC. VCC only needs to be decoupled with a ceramic capacitor less than 1µF. After the system starts up, VCC is powered by the higher value of IN1, IN2, or VOUT internally.

#### **Dual Input - IN1 and IN2**

IN1 is a high voltage input pin, which can support up to 22V voltage, but the part will be in input overvoltage shutdown mode when IN1>5.75V.

IN2 is a low voltage input pin, which supports 5.5V maximum operation voltage.

OR\_OUT is the output of the IN1 and IN2 ORing. The two sets of ORing MOSFETs (IN1 to OR\_OUT, IN2 to OR\_OUT) are integrated. The MP5461 employs soft-start control for both IN1 or IN2 to OR\_OUT start-up.

If the power source for one channel drops, the fast turn-off protection minimizes the reverse current.

SEL is the power path selection input. Applying low voltage or floating SEL can select the IN1 to OR\_OUT power path. Applying a high voltage on SEL can select the IN2 to OR\_OUT power path.

If only one power input is available, the MP5461 will auto use that power input to supply OR\_OUT. For additional details on the SEL input state, refer to Table 1.

#### Power Path Indication - STATUS

STATUS is an open drain output. It indicates if the VIN1 or VIN2 channel is selected. When VIN1 is selected, or there is no power supply at VIN1 and VIN2, STATUS is an open drain output; when VIN2 is selected, STATUS is pulled low. Refer to the truth table.

#### **Buck - Boost Operation**

The output voltage is sensed via an internal resistor divider from the output to ground. The voltage difference between the VOUT feedback voltage and the internal reference is amplified by the error amplifier to generate a control signal ( $V_{C-Buck}$ ). By comparing  $V_{C-Buck}$  with the internal current ramp signal (the sensed SWA's current with slope compensation) through the buck comparator, a pulse-width modulation (PWM) control signal for the buck leg (SWA, SWB) is generated.

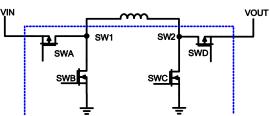

Another control signal ( $V_{\text{C-Boost}}$ ) is derived from  $V_{\text{C-Buck}}$  through the level shift. Similarly,  $V_{\text{C-Boost}}$  is compared with the same ramp signal through the boost comparator and generates a PWM control signal for the boost leg (SWC, SWD). The switch topology for the buck-boost converter is shown in Figure 2.

Figure 2: Buck-Boost Switch Topology

#### **Buck Region (VIN > VOUT)**

When the input voltage is significantly higher than the output voltage, the converter can deliver energy to the load within SWA's maximum duty cycle by switching SWA and SWB. The converter operates in buck mode. In this condition, SWD remains on and SWC remains off.  $V_{\text{C-Buck}}$  compares the current ramp signal and generates a PWM output. Therefore, SWA/SWB is pulsewidth modulated to produce the required duty cycle and eventually supports the output voltage.

#### **Buck-Boost Region (VIN ≈ VOUT)**

When VIN is close to VOUT, the converter is unable to provide enough energy to the load due to SWA's maximum duty cycle, so the current ramp signal cannot trigger  $V_{\text{C-Buck}}$  in the first cycle, and SWA remains on with a 100% duty cycle. If SWB is not turned on in the first cycle, boost begins working in the second cycle (SWC switches in the second cycle), and an offset voltage is added to the current ramp signal to allow it to reach  $V_{\text{C-Buck}}$ . SWC turns off when the current ramp signal intersects with  $V_{\text{C-Boost}}$  in the second cycle, and SWD conducts the inductor current when SWC is off. This is called boost operation.

SWA turns off when the current ramp signal intersects with  $V_{\text{C-Buck}}$  in the second cycle, and SWB turns on to conduct the inductor current after SWA turns off. This is called buck operation.

If SWB turns on in the second cycle, the boost operation (SWC on) is disabled in the following cycle. If SWA continues to conduct with 100% duty in the second cycle, boost operation is also enabled in the following duty cycle. SWA/SWB and SWC/SWD switch during this condition simultaneously. This is called buck-boost mode.

#### **Boost Region (VIN < VOUT)**

When the input voltage is significantly lower than the output voltage, the control voltage ( $V_{C\text{-Buck}}$ ) is always higher than the current ramp signal. The offset voltage is added to the current signal, so SWB cannot turn on in all cycles. The boost operation (SWC on) is enabled in every cycle based on the logic, so only SWC and SWD switch. This is called boost mode. In this condition, SWC/SWD is pulse-width modulated to produce the required duty cycle and eventually support the output regulation voltage.

#### Internal Soft Start (SS)

When EN is active and OR\_OUT is above the UVLO rising threshold, the MP5461 buck-boost starts up with a soft-start function. The internal soft-start (SS) signal ramps up and controls the feedback reference voltage.

#### OCP/SCP

The MP5461 employs peak current limits through switch A current sensing. The current limit is 2.5A (typical).

In an overload or short-circuit condition, VOUT drops due to the steady-state switching current limit. If VOUT drops below 60% of its normal output, the MP5461 stops switching and recovers after ~12ms with hiccup mode protection. After the switching stops in hiccup protection, the internal soft-start signal is clamped to  $V_{FB}$  + 0.3V, where  $V_{FB}$  is the divided voltage from the residual VOUT. This is used to make the soft start-up smooth when the MP5461 recovers from hiccup protection.

During the soft-start time, the MP5461 blanks during hiccup protection. After the soft-start time is finished, if VOUT is still lower than 60% of the normal voltage, the MP5461 resumes hiccup mode. If VOUT rises above 60% of the normal value, the MP5461 enters normal operation.

#### **OVP**

The MP5461 employs output over-voltage protection. A fast comparator will sense the output voltage condition. Once it's triggered, the MP5461 will stop switching, and a 1k internal resistor will be switched on to discharge the output.

#### **APPLICATION INFORMATION**

#### **Component Selection**

#### **Selecting the Inductor**

As a buck-boost topology circuit, the inductor must support buck application with the maximum input voltage and boost application with the minimum input voltage. Two critical inductance values can be calculated according to the buck and boost mode current ripple using equation (1) and equation (2).

$$L_{\text{MIN-BUCK}} = \frac{V_{\text{OUT}} \times (V_{\text{IN(MAX)}} - V_{\text{OUT}})}{V_{\text{IN(MAX)}} \times F_{\text{REQ}} \times \Delta I_{L}}$$

(1)

$$L_{\text{MIN-BOOST}} = \frac{V_{\text{IN(MIN)}} \times (V_{\text{OUT}} - V_{\text{IN(MIN)}})}{V_{\text{OUT}} \times F_{\text{REQ}} \times \Delta I_{L}}$$

(2)

#### Where:

FREQ is the switching frequency

$\Delta I_L$  is the peak-to-peak inductor current ripple. As a rule of thumb, the peak-to-peak ripple can be set at 0.2A to 1A to achieve better balance of the BOM cost, output ripple, and efficiency. The minimum inductor value for application should be the highest value between the results from equation (1) and equation (2).

In addition to the inductance value, the inductor must support peak current based on equation (3) and equation (4) to avoid saturation.

$$I_{PEAK-BUCK} = I_{OUT} + \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{2 \times V_{IN(MAX)} \times F_{REQ} \times L}$$

(3)

$$I_{\text{PEAK-BOOST}} = \frac{V_{\text{OUT}} \times I_{\text{OUT}}}{\eta \times V_{\text{IN(MIN)}}} + \frac{V_{\text{IN(MIN)}} \times (V_{\text{OUT}} - V_{\text{IN(MIN)}})}{2 \times V_{\text{OUT}} \times F_{\text{REQ}} \times L}$$

(4)

Where  $\eta$  is the estimated efficiency of the MP5461.

Choose a proper inductor to make sure the inductor current won't trigger a peak current limit and valley current limit.

#### **Input and Output Capacitor Selection**

It is recommended to use ceramic capacitors with low ESR as input and output capacitors in order to filter any disturbance present in the input line and to obtain stable operation.

Minimum values of  $1\mu F$  for input 1, and  $1\mu F$  for input 2 as well as  $2x22\mu F$  for output capacitors are needed to achieve optimal performance.

The input and output capacitors must be placed as close to the device as possible.

#### PC Board Layout (8)

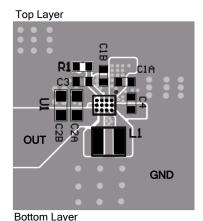

Efficient PCB layout is critical for standard operation and thermal dissipation. Refer to Figure 3 and the PCB layout guidelines below to ensure an effective layout design:

- 1) Place the OR\_OUT capacitor and VOUT capacitor as close as possible to the OR\_OUT and OUT pin as possible.

- 2) Use a large ground plane directly connected to GND. Add lots of GND vias to connect Cout's GND node and OR\_OUT capacitor's GND.

- 3) Connect AGND to VCC capacitor's GND node by a Kelvin sense trace.

- 4) Place the VCC decoupling capacitor as close as possible to VCC.

#### Notes:

(8) The recommended layout is based on the typical application circuit on the next page (see Figure 4).

IN2

IN1

Connect AGND to VCC cap GND node

GND

Figure 3: PC Board Layout

# **TYPICAL APPLICATION CIRCUITS**

Figure 4: Typical application circuit with fixed 3.3V output voltage

#### **PACKAGE INFORMATION**

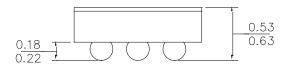

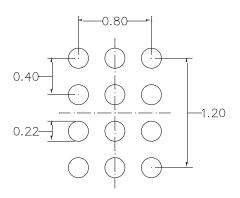

#### CSP-12 (1.4mmx1.8mm)

#### **SIDE VIEW**

#### **RECOMMENDED LAND PATTERN**

#### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) BALL COPLANARITY SHALL BE 0.05 MILLIMETER MAX.

- 3) JEDEC REFERENCE IS MO-211.

- 4) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.