# Wide Input Range, 4.5A, I<sup>2</sup>C-Controlled SW Charger with NVDC Power Path and USB OTG and Enhanced ADC

#### DESCRIPTION

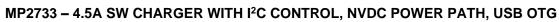

The MP2733 is a 4.5A, highly integrated switch-mode battery charger management device for single-cell Li-ion or Li-polymer batteries. This device works with narrow voltage DC (NVDC) system power path management, and is well-suited for a variety of applications, including smartphones, tablets, wireless cameras, and other portable devices. Its low-impedance power path optimizes efficiency, reduces battery charging time, and extends battery life. The I<sup>2</sup>C interface allows the device to be flexibly controlled with configurable charging and system settings.

The MP2733 supports a wide range of input sources, including standard USB host ports and high-powered wall adapters with fast charge capabilities. The MP2733 provides USB input type detection via the DP/DM pins.

The device supports USB On-the-Go (OTG) operation by supplying 5V on the input bus, with an output current limit up to 3A.

The MP2733 initiates and completes a charging cycle without software control. It automatically detects the battery voltage and charges the battery in different stages. Charging automatically terminates when a full charge is detected. When the charged battery drops below the recharge threshold, the charger automatically begins another charging cycle.

The charger provides various safety features for battery charging and system operations, including a charging safety timer, battery temperature monitoring, and over-voltage protection (OVP), and over-current protection (OCP). If a fault occurs, the charger asserts an INT signal to the host. The device provides BATTFET disable control to enter shipping mode, as well as system reset functionality via the DISC pin.

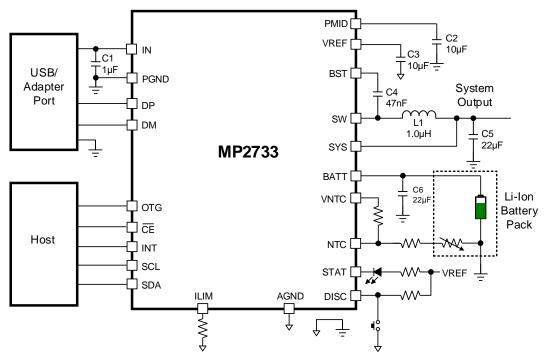

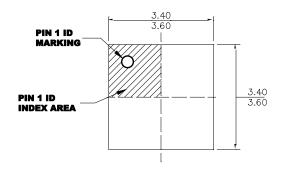

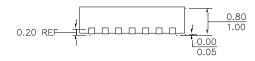

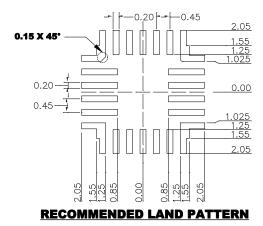

The MP2733 is available in a QFN-26 (3.5mmx3.5mm) package.

#### **FEATURES**

- 3.7V to 16V Operating Input Voltage Range

- Up to 22V Sustainable Voltage

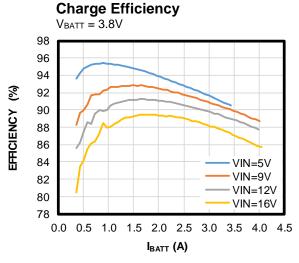

- High-Efficiency, 4.5A, 1.35MHz Buck Charger with Up to 92% Charge Efficiency with 3A Charge Current:

- Configurable D+/D- for Flexible Fast Charge Protocol Support

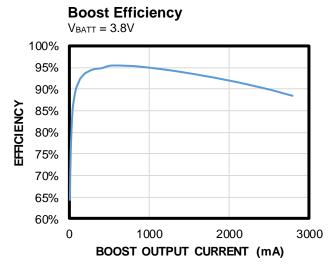

- USB OTG with 4.8V to 5.5V Adjustable Output: Up to 3A Output, Up to 93% Efficiency with 1.5A Output

- NVDC Power Path Management

- Instant-On Works with No Battery or Deeply Discharged Battery

- Ideal Diode Operation in Battery Supplement Mode

- High Battery Discharge Efficiency with 14mΩ BATTFET Up to 8.5A

- I<sup>2</sup>C Interface for Flexible System Parameter Setting and Status Reporting

- Fully Integrated MOSFETs, Current Sensing

- Dedicated DISC Pin to Control Shipping Mode and System Reset

- 13µA Low Battery Leakage Current in Shipping Mode

- Integrated ADC Monitors Input Voltage and Current, Battery Voltage, Charge Current, System Voltage, and Battery Temperature

- Charging Status Indicator

- Safety Features: Configurable JEITA for Battery Temp Protection in Charge Mode, Battery Charging Safety Timer, Thermal Regulation and Shutdown, Watchdog Monitoring I<sup>2</sup>C, and Input/System OVP

- Available in a QFN-26 (3.5mmx3.5mm) Package

#### **APPLICATIONS**

- Tablet PCs

- Smartphones

- Wireless Cameras

- Other Portable Devices

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

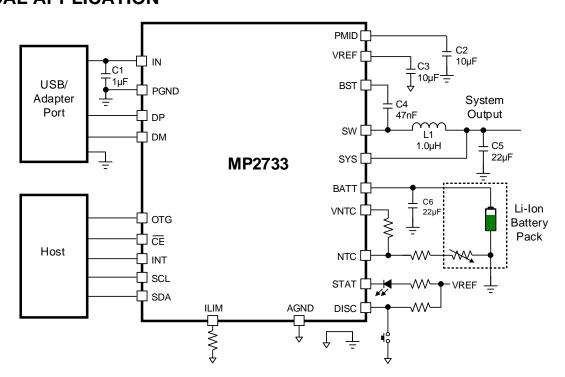

# **TYPICAL APPLICATION**

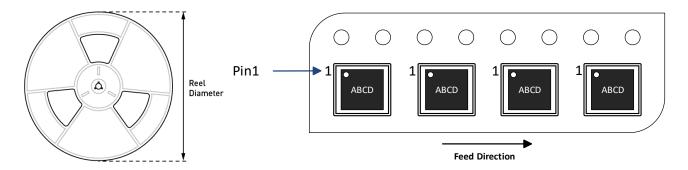

#### ORDERING INFORMATION

| Part Number*     | Package              | Top Marking | MSL Rating |

|------------------|----------------------|-------------|------------|

| MP2733GQC-xxxx** |                      |             |            |

| MP2733GQC-0000   | QFN-26 (3.5mmx3.5mm) | See Below   | 1          |

| MP2733GQC-0001   |                      |             |            |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP2733GQC-xxxx-Z).

#### **TOP MARKING**

BQEYW LLLLL

BQE: Product code of MP2733GQC

Y: Year code W: Week code LLLLL: Lot number

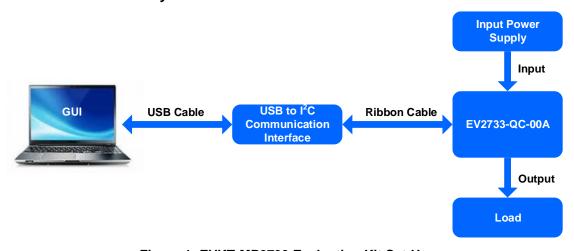

#### **EVALUATION KIT EVKT-MP2733**

EVKT-MP2733 kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                              | Quantity |

|---|--------------------|---------------------------------------------------------------------------------------------------|----------|

| 1 | EV2733-QC-00A      | MP2733 evaluation board                                                                           | 1        |

| 2 | EVKT-USBI2C-02-BAG | Includes one USB to I <sup>2</sup> C communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | Online resources   | Include datasheet, user guide, product brief, and GUI                                             | 1        |

#### Order directly from MonolithicPower.com or our distributors.

Figure 1: EVKT-MP2733 Evaluation Kit Set-Up

<sup>\*\*&</sup>quot;xxxx" is the register setting option. The factory default code for general applications is "0000". The factory default code for solar or MPPT applications is "0001". This content can be viewed in the I<sup>2</sup>C Register Map on page 31 and OTP Map on page 46. Contact an MPS FAE to obtain an "xxxx" value.

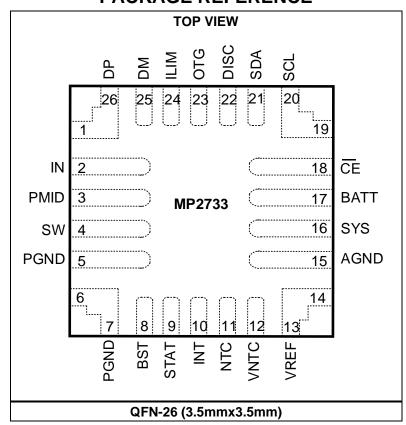

# **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Pin#    | Name | Туре | Description                                                                                                                                                                                                                                                               |

|---------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 26   | DP   | I/O  | Positive pin of the USB data line pair.                                                                                                                                                                                                                                   |

| 2       | IN   | Р    | <b>Power input of the IC.</b> Place a 1µF ceramic capacitor from IN to PGND, as close as possible to the IC.                                                                                                                                                              |

| 3       | PMID | Р    | Internal power pin. Connect PMID to the drain of the reverse-blocking MOSFET and the drain of the high-side MOSFET (HS-FET). Bypass PMID with a $10\mu F$ capacitor from PMID to PGND, placed as close as possible to the IC.                                             |

| 4       | SW   | Р    | Switching node.                                                                                                                                                                                                                                                           |

| 5, 6, 7 | PGND | Р    | Power ground.                                                                                                                                                                                                                                                             |

| 8       | BST  | Р    | <b>Bootstrap pin.</b> Connect a 47nF bootstrap capacitor between the BST and SW pins to form a floating supply across the power switch driver. This drives the power switch's gate above the supply voltage.                                                              |

| 9       | STAT | 0    | Open-drain charge status output to indicate various charger operations. Connect STAT to VREF using a $10k\Omega$ resistor.                                                                                                                                                |

| 10      | INT  | 0    | <b>Open-drain interrupt output</b> . The INT pin can send charging status and fault interrupt signals to the host.                                                                                                                                                        |

| 11      | NTC  | I    | <b>Temperature-sense input</b> . Connect a negative temperature coefficient thermistor to the NTC pin. Configure the hot and cold temperature windows with a resistor divider connected from VNTC to NTC to AGND. Charging is suspended when the NTC pin is out of range. |

| 12      | VNTC | Р    | <b>Pull-up voltage bias.</b> The VNTC pin is the pull-up voltage bias of the NTC comparator resistive divider for both the feedback and the reference.                                                                                                                    |

| 13, 14  | VREF | Р    | <b>PWM low-side driver output.</b> Connect a $10\mu F$ ceramic capacitor from VREF to AGND, placed as close as possible to the IC.                                                                                                                                        |

| 15      | AGND | Р    | Analog ground.                                                                                                                                                                                                                                                            |

| 16      | SYS  | Р    | System output. Connect a 22 $\mu$ F ceramic capacitor from SYS to PGND, placed as close as possible to the IC.                                                                                                                                                            |

| 17      | BATT | Р    | <b>Battery positive terminal.</b> Connect a 22µF ceramic capacitor from BATT to PGND, placed as close as possible to the IC.                                                                                                                                              |

| 18      |      |      | Active low charge enable pin. Battery charging is enabled when the                                                                                                                                                                                                        |

| 10      | CE   | ı    | corresponding register is set to active and the CE pin is low.                                                                                                                                                                                                            |

| 19, 20  | SCL  | I    | <b>I</b> <sup>2</sup> <b>C</b> interface clock. Connect SCL to the logic rail through a 10kΩ resistor.                                                                                                                                                                    |

| 21      | SDA  | I/O  | <b>I</b> <sup>2</sup> <b>C</b> interface data. Connect SDA to the logic rail through a 10kΩ resistor.                                                                                                                                                                     |

| 22      | DISC | ı    | <b>Battery disconnection control pin.</b> The DISC pin can be used for shipping mode and system resetting.                                                                                                                                                                |

| 23      | OTG  | I    | <b>Boost mode enable control pin.</b> The On-The-Go (OTG) function is enabled via the I <sup>2</sup> C. During boost operation, the OTG pin can go low to suspend boost operation.                                                                                        |

| 24      | ILIM | I    | <b>Configurable input current limit.</b> To set the maximum input current limit, connect a resistor from ILIM to ground. The actual input current limit is the lower value set by the ILIM pin or the I <sup>2</sup> C.                                                   |

| 25      | DM   | I/O  | Negative pin of the USB data line pair.                                                                                                                                                                                                                                   |

#### **ABSOLUTE MAXIMUM RATINGS** (1)

#### Recommended Operating Conditions (3)

| V <sub>IN</sub> to GND                    | 2 7\/ to 16\/ (4) |

|-------------------------------------------|-------------------|

|                                           |                   |

| I <sub>IN</sub>                           | Up to 3.25A       |

| I <sub>SYS</sub>                          | Úp to 4.5A        |

| lcc                                       |                   |

| V <sub>BATT</sub>                         | Up to 4.67V       |

| IDSCHG (CONTINUOUS)                       | Úp to 8.5A        |

| IDSCHG (PULSE)                            |                   |

| Operating junction temp (T <sub>J</sub> ) |                   |

# **Thermal Resistance** (5) **θ**<sub>JA</sub> **θ**<sub>JC</sub> QFN-26 (3.5mmx3.5mm).......48......11... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) The inherent switching noise voltage should not exceed the absolute maximum rating on either the BST or SW pin. A tight layout minimizes switching loss.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                                  | Symbol                   | Condition                                                                                                                                                | Min  | Тур  | Max  | Units    |

|------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| Step-Down Converter                                        | -                        |                                                                                                                                                          | •    |      | ı    | <u> </u> |

| Input voltage                                              | V <sub>IN</sub>          |                                                                                                                                                          | 3.7  |      | 16   | V        |

| Input suspend current                                      | l <sub>IN_</sub> sus     | V <sub>IN</sub> > V <sub>IN_UVLO</sub> , V <sub>IN</sub> > V <sub>BATT</sub> ,<br>suspend mode, EN_HIZ = 1                                               |      | 1    | 1.5  | mA       |

| Input quiescent current                                    | l <sub>IN_Q</sub>        | $V_{\text{IN}} > V_{\text{IN\_UVLO}}, V_{\text{IN}} > V_{\text{BATT}}, \\ V_{\text{BATT}} = 3.6 V, \text{ converter switching}, \\ I_{\text{SYS}} = 0 A$ |      | 4    |      | IIIA     |

| Input under-voltage lockout (UVLO) threshold               | V <sub>IN_UVLO</sub>     | V <sub>IN</sub> falling                                                                                                                                  |      | 3    | 3.2  | V        |

| Input UVLO threshold hysteresis                            |                          | V <sub>IN</sub> rising                                                                                                                                   |      | 200  |      | mV       |

| Input vs. battery voltage                                  | V <sub>HDRM</sub>        | V <sub>IN</sub> rising                                                                                                                                   | 230  | 300  | 370  | mV       |

| headroom                                                   | VHDRM                    | V <sub>IN</sub> falling                                                                                                                                  | 120  | 190  | 260  | mV       |

| Input over-voltage                                         |                          | V <sub>IN</sub> rising                                                                                                                                   | 5.8  | 6    | 6.3  |          |

| protection (OVP) threshold                                 | Vin_ovlo                 | V <sub>IN</sub> rising, for V <sub>IN</sub> > 5V                                                                                                         | 16.2 | 16.7 | 17.2 | V        |

| Input OVP threshold hysteresis                             |                          | V <sub>IN</sub> falling                                                                                                                                  |      | 380  |      | mV       |

| Internal reverse blocking MOSFET on resistance             | Ron_q1                   | Measure from IN to PMID                                                                                                                                  |      | 20   |      | mΩ       |

| High-side MOSFET (HS-FET) on resistance                    | R <sub>ON_Q2</sub>       | Measure from PMID to SW                                                                                                                                  |      | 25   |      | mΩ       |

| Low-side MOSFET (LS-FET) on resistance                     | R <sub>ON_Q3</sub>       | Measure from SW to PGND                                                                                                                                  |      | 25   |      | mΩ       |

| Switching frequency                                        | fsw                      | V <sub>BATT</sub> = 3.7V, I <sub>CHG</sub> = 2A,<br>REG0Ah, bit[7] = 0                                                                                   | 1.1  | 1.35 | 1.6  | MHz      |

| SYS Output                                                 |                          |                                                                                                                                                          | _    |      |      |          |

| Minimum system regulation voltage (I <sup>2</sup> C)       | Vsys_reg_min             | VSYS_MIN + VTRACK, ISYS = 0,<br>VBATT = 3.4V, REG04h, bits[3:1] =<br>110, REG04h, bit[0] = 1                                                             |      | 3.82 |      | V        |

| Pottory tracking valtage                                   | V                        | REG04h, bit[0] = 0                                                                                                                                       |      | 100  |      | mV       |

| Battery tracking voltage                                   | VTRACK                   | REG04h, bit[0] = 1                                                                                                                                       |      | 150  |      | mV       |

| Ideal diode forward voltage in supplement mode             | V <sub>FWD</sub>         | 10mA discharge current                                                                                                                                   |      | 20   |      | mV       |

| SYS vs. BATT comparator                                    | V <sub>SYS_GT_BATT</sub> | V <sub>SYS</sub> falling to enter ideal diode mode                                                                                                       |      | -20  |      | mV       |

| SYS vs. BATT comparator hysteresis                         |                          | V <sub>SYS</sub> rising to exit ideal diode mode                                                                                                         |      | 50   |      | mV       |

| Battery good comparator (threshold compared with Vsys_MIN) | V <sub>BATT_</sub> GD    | V <sub>BATT</sub> rising to the BATTFET being fully turned on                                                                                            |      | 60   |      | mV       |

| Battery good comparator hysteresis                         |                          | VBATT falling                                                                                                                                            |      | 100  |      | mV       |

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                               | rameter Symbol Condition |                                                                                                                                                           | Min  | Тур        | Max  | Units |

|---------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|------|-------|

| Battery Charger                                         |                          |                                                                                                                                                           |      |            |      |       |

| Battery charge voltage regulation (I <sup>2</sup> C)    | V <sub>BATT_REG</sub>    | Depends on the I <sup>2</sup> C setting                                                                                                                   | 3.4  |            | 4.67 | V     |

| Battery charge voltage regulation accuracy              | VBATT_REG_<br>ACC        | REG07h, bits[7:1] = 1010000,<br>VBATT_REG = 4.2V<br>REG07h, bits[7:1] = 1011111,<br>VBATT_REG = 4.35V<br>REG07h, bits[7:1] = 1100100,<br>VBATT_REG = 4.4V | -0.5 |            | +0.5 | %     |

| Fast charge current (I <sup>2</sup> C)                  | Icc                      | Depends on the I <sup>2</sup> C setting                                                                                                                   | 320  |            | 4520 | mA    |

| - det endige edinent (i e)                              | 100                      | Icc, REG05h, bits[6:0] = 0000100,<br>VBATT = 3.8V                                                                                                         | 442  | 500        | 558  | mA    |

| Fast charge current accuracy                            | loo soo                  | I <sub>CC</sub> , REG05h,bits[6:0] = 0100110,<br>V <sub>BATT</sub> = 3.8V                                                                                 | 1739 | 1850       | 1951 | mA    |

| rasi charge current accuracy                            | Icc_acc                  | Icc, REG05h,bits[6:0] = 1000011,<br>V <sub>BATT</sub> = 3.8V                                                                                              | 2849 | 3000       | 3151 | mA    |

|                                                         |                          | Icc, REG05h,bits[6:0] = 1101001,<br>VBATT = 3.8V                                                                                                          | 4294 | 4520       | 4750 | mA    |

| Pre-charge to fast charge threshold (I <sup>2</sup> C)  | V <sub>BATT_PRE</sub>    | V <sub>BATT</sub> rising, REG05h, bit[7] = 1                                                                                                              | 2.8  | 3.0        | 3.1  | V     |

| Pre-charge to fast charge hysteresis                    |                          | V <sub>BATT</sub> falling                                                                                                                                 |      | 160        |      | mV    |

| Trickle charge to pre-charge threshold                  | V <sub>BATT_TC</sub>     | VBATT rising                                                                                                                                              | 1.9  | 2.0        | 2.1  | V     |

| Trickle charge to pre-charge threshold hysteresis       |                          | V <sub>BATT</sub> falling                                                                                                                                 |      | 50         |      | mV    |

| Trickle-charge current                                  | I <sub>TC</sub>          | V <sub>BATT</sub> = 1.8V, I <sub>PRE</sub> , REG06h,bit[4] = 1<br>V <sub>BATT</sub> = 1.8V, I <sub>PRE</sub> , REG06h,bit[4] = 0                          |      | 185<br>145 |      | mA    |

| Pre-charge current (I <sup>2</sup> C)                   | I <sub>PRE</sub>         | Depends on the I <sup>2</sup> C setting                                                                                                                   | 150  |            | 750  | mA    |

| Pre-charge current accuracy                             |                          | V <sub>BATT</sub> = 2.6V,<br>REG06h, bits[7:4] = 0010                                                                                                     | 182  | 225        | 268  | mA    |

| Charge termination current threshold (I <sup>2</sup> C) | I <sub>TERM</sub>        | Depends on the I <sup>2</sup> C setting                                                                                                                   | 120  |            | 720  | mA    |

| Termination current accuracy                            |                          | V <sub>BATT_REG</sub> = 4.2V,<br>REG06h, bits[3:0] = 0110                                                                                                 | 298  | 360        | 422  | mA    |

| Charge termination deglitch time                        | tterm_dgl                |                                                                                                                                                           |      | 200        |      | ms    |

| Auto-recharge voltage threshold below VBATT_REG         | V <sub>RECH</sub>        | REG07h, bit[0] = 0                                                                                                                                        |      | 110        |      | mV    |

| Auto-recharge deglitch time                             | trech_dgl                |                                                                                                                                                           |      | 200        |      | ms    |

| BATTFET on resistance                                   | R <sub>ON_Q4</sub>       | V <sub>BATT</sub> = 3.8V                                                                                                                                  |      | 14         |      | mΩ    |

| Battery discharge current limit                         | IDSCHG_LMT               | V <sub>IN</sub> = 0V, V <sub>BATT</sub> = 3.8V, OTG disabled, I <sub>SYS</sub> rising                                                                     | 8.5  |            |      | Α     |

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                           | Symbol                | Condition                                                                                          | Min  | Тур   | Max  | Units |

|-----------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|------|-------|------|-------|

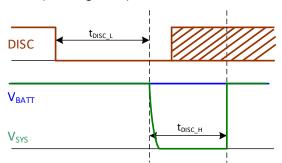

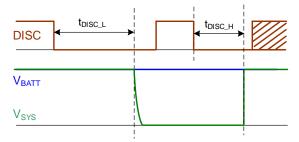

| Battery discharge function                          | toisc                 | DISC pin low time to turn off the battery discharge function, REG0Ah, bits[1:0] = 00               |      | 8     |      | S     |

| controlled by the DISC pin                          | tbisc                 | Battery discharge off time to turn on<br>the battery discharge function,<br>REG0Ah, bits[3:2] = 00 |      | 0.5   |      | S     |

| Input Voltage and Input Curren                      | t Regulation          | า                                                                                                  |      |       |      |       |

| Input minimum voltage regulation (I <sup>2</sup> C) | V <sub>IN_MIN</sub>   |                                                                                                    | 3.7  |       | 15.2 | V     |

| Input minimum voltage regulation accuracy           | VIN_MIN_ACC           | REG01h, bits[6:0] = 0000110,<br>$V_{IN\_REG} = 4.3V$                                               | -3   |       | +3   | %     |

|                                                     |                       | USB500                                                                                             | 400  | 450   | 500  |       |

|                                                     |                       | USB900                                                                                             | 750  | 825   | 900  |       |

|                                                     |                       | 1A                                                                                                 | 840  | 920   | 1000 |       |

|                                                     |                       | CDP or 1.5A                                                                                        | 1270 | 1400  | 1500 |       |

| Input current limit                                 | I <sub>IN_LIM</sub>   | DCP                                                                                                | 1570 | 1690  | 1800 | mA    |

|                                                     |                       | 2A                                                                                                 | 1750 | 1880  | 2000 |       |

|                                                     |                       | 2.1A                                                                                               | 1840 | 1970  | 2100 |       |

|                                                     |                       | 2.4A                                                                                               | 2050 | 2240  | 2400 |       |

|                                                     |                       | 3A                                                                                                 | 2640 | 2800  | 3000 |       |

| Protection                                          |                       |                                                                                                    |      |       |      |       |

| Battery over-voltage protection (OVP) threshold     | V <sub>BATT_OVP</sub> | Rising, compared to VBATT_REG                                                                      |      | 103.5 |      | %     |

| Battery OVP threshold hysteresis                    |                       | Compared to VBATT_REG                                                                              |      | 1.5   |      | %     |

| Thermal regulation                                  | T <sub>J_REG</sub>    | T <sub>J_REG</sub> , REG02h, bits[3:2] = 11                                                        |      | 112   |      | °C    |

| Thermal shutdown threshold (6)                      | T <sub>J_SHDN</sub>   | T <sub>J</sub> rising                                                                              |      | 150   |      | ů     |

| Thermal shutdown hysteresis (6)                     |                       |                                                                                                    |      | 20    |      | °C    |

| NTC float threshold                                 | $V_{FLT}$             | As a percentage of VNTC                                                                            |      | 95    |      | %     |

| NTC float threshold hysteresis                      |                       | As a percentage of VNTC                                                                            |      | 3.6   |      | %     |

| NTC low temp rising threshold                       | Vcold                 | As a percentage of VNTC                                                                            | 71   | 72    | 73   | %     |

| NTC low temp rising threshold hysteresis            |                       | As a percentage of VNTC                                                                            |      | 1.3   |      | %     |

| NTC cool temp rising threshold                      | Vcool                 | As a percentage of VNTC                                                                            | 59   | 60    | 61   | %     |

| NTC cool temp rising threshold hysteresis           |                       | As a percentage of VNTC                                                                            |      | 1.3   |      | %     |

| NTC warm temp falling threshold                     | $V_{WARM}$            | As a percentage of VNTC                                                                            | 39.3 | 40.3  | 41.3 | %     |

| NTC warm temp falling threshold hysteresis          |                       | As a percentage of VNTC                                                                            |      | 1.5   |      | %     |

| NTC hot temp falling threshold                      | V <sub>НОТ</sub>      | As a percentage of VNTC                                                                            | 35.3 | 36.3  | 37.3 | %     |

#### Note:

6) Guaranteed by design.

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                          | Symbol                        | Condition                                                                                                      | Min  | Тур  | Max  | Units |

|----------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| NTC hot temp falling threshold hysteresis          |                               | As a percentage of VNTC                                                                                        |      | 1.5  |      | %     |

| VREF LDO                                           |                               |                                                                                                                |      |      |      |       |

| VREF LDO output voltage                            | V <sub>REF</sub>              | V <sub>IN</sub> = 5V, I <sub>VREF</sub> = 20mA                                                                 |      | 3.6  |      | V     |

| VREF LDO current limit                             | I <sub>REF_LMT</sub>          | V <sub>VREF</sub> = 3.3V                                                                                       | 40   |      |      | mA    |

| <b>Battery Discharge Operation</b>                 |                               |                                                                                                                |      |      |      |       |

| Battery operating range                            | V <sub>BATT</sub>             |                                                                                                                | 2.6  |      | 4.75 | V     |

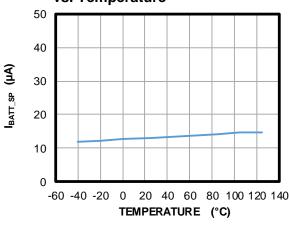

| Battery current in shipping mode                   | I <sub>BATT_SP</sub>          | V <sub>IN</sub> < V <sub>IN_UVLO</sub> , V <sub>BATT</sub> = 4.2V,<br>BATTFET off                              |      | 13   | 16   | μΑ    |

|                                                    |                               | V <sub>IN</sub> < V <sub>IN_UVLO</sub> , V <sub>BATT</sub> = 4.2V,<br>BATTFET on, OTG disabled                 |      | 40   | 47   | μΑ    |

| Battery quiescent current                          | I <sub>BATT_Q</sub>           | V <sub>IN</sub> < V <sub>IN_UVLO</sub> , V <sub>BATT</sub> = 4.2V,<br>BATTFET on, OTG enabled                  |      | 5.0  |      | mA    |

|                                                    |                               | V <sub>IN</sub> < V <sub>IN_UVLO</sub> , V <sub>BATT</sub> = 4.2V,<br>BATTFET on, OTG disabled,<br>ADC enabled |      | 2    |      | mA    |

| OTG output voltage                                 | VIN_DSCHG                     | REG03h, bits[5:3] = 011, lotg = 0A                                                                             |      | 5.07 |      | V     |

| OTG output voltage accuracy                        |                               | As a percentage of V <sub>IN_OTG</sub> ,<br>Iotg = 0A                                                          | -2   |      | +2   | %     |

| Pottory operation LIVI O                           | V                             | V <sub>BATT</sub> falling                                                                                      | 2.35 | 2.45 | 2.55 | V     |

| Battery operation UVLO                             | VBATT_UVLO                    | V <sub>BATT</sub> rising                                                                                       | 2.68 | 2.8  | 2.92 | V     |

| Battery operation UVLO for                         | V <sub>BATT_UVLO</sub>        | V <sub>BATT</sub> falling                                                                                      | 2.45 | 2.55 | 2.65 | V     |

| OTG                                                | _OTG                          | V <sub>BATT</sub> rising                                                                                       |      | 3.0  |      | V     |

| OTG output voltage protection threshold            | V <sub>INOVP</sub> _<br>DSCHG | V <sub>BATT</sub> = 3.7V, OTG is enabled, force a voltage at IN until REG0Dh, bit[6] = 1                       |      | 6.15 |      | >     |

| OTG output voltage protection threshold hysteresis |                               |                                                                                                                |      | 330  |      | mV    |

|                                                    |                               | REG03h, bits[2:0] = 000,<br>V <sub>BATT</sub> = 3.7V                                                           | 0.5  | 0.6  | 0.7  |       |

| OTG output current limit (I <sup>2</sup> C)        |                               | REG03h, bits[2:0] = 011,<br>V <sub>BATT</sub> = 3.7V                                                           | 1.5  | 1.65 | 1.8  | ۸     |

| oro output current limit (i o)                     | IIN_DSCHG                     | REG03h, bits[2:0] = 101,<br>V <sub>BATT</sub> = 3.7V                                                           | 2.1  | 2.25 | 2.4  | A     |

|                                                    |                               | REG03h, bits[2:0] = 111,<br>VBATT = 3.7V                                                                       | 3.0  | 3.15 | 3.3  |       |

| Analog-to-Digital Converter (                      | ADC)                          |                                                                                                                |      |      |      |       |

| Resolution                                         | RES                           |                                                                                                                |      | 8    |      | bits  |

| Input voltage range                                | V <sub>IN</sub>               |                                                                                                                | 3.6  |      | 15.3 | V     |

| Input voltage LSB                                  | V <sub>IN_RES</sub>           |                                                                                                                |      | 60   |      | mV    |

| Input voltage accuracy                             | V <sub>IN_ACC</sub>           | V <sub>IN</sub> = 5V                                                                                           |      | 2    |      | LSB   |

| Battery voltage range                              | V <sub>BATT</sub>             |                                                                                                                | 0    |      | 5.1  | V     |

| Battery voltage LSB                                | V <sub>BATT_RES</sub>         |                                                                                                                |      | 20   |      | mV    |

| Battery voltage accuracy                           | V <sub>BATT_ACC</sub>         | V <sub>BATT</sub> = 3.8V                                                                                       |      | 2    |      | LSB   |

| Charge current range                               | Існв                          |                                                                                                                | 0    |      | 5.66 | Α     |

$V_{IN} = 5V$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                             | Symbol               | Condition                                | Min  | Тур   | Max  | Units |

|---------------------------------------|----------------------|------------------------------------------|------|-------|------|-------|

| Charge current LSB                    | I <sub>CHG_RES</sub> |                                          |      | 17.5  |      | mA    |

| Charge current accuracy               | I <sub>CHG_ACC</sub> | Charge mode, I <sub>CHG</sub> = 1.84A    |      | 3     |      | LSB   |

| System voltage range                  | Vsys                 |                                          | 0    |       | 5.1  | V     |

| System voltage LSB                    | V <sub>SYS_RES</sub> |                                          |      | 20    |      | mV    |

| System voltage accuracy               | Vsys_acc             | V <sub>SYS</sub> = 3.8V                  |      | 2     |      | LSB   |

| Input current range                   | I <sub>IN</sub>      |                                          | 0    |       | 3.39 | Α     |

| Input current LSB                     | I <sub>IN_RES</sub>  |                                          |      | 13.3  |      | mA    |

| Input current accuracy                | I <sub>IN_ACC</sub>  | I <sub>IN</sub> = 500mA                  |      | 4     |      | LSB   |

| NTC voltage range                     | V <sub>NTC</sub>     |                                          | 0    |       | 100  | %     |

| NTC voltage LSB                       | V <sub>NTC_RES</sub> |                                          |      | 0.392 |      | %     |

| NTC voltage accuracy                  | V <sub>NTC_ACC</sub> | V <sub>NTC</sub> = 50%                   |      | 2     |      | LSB   |

| DP/DM USB Detection                   | <u>-</u>             |                                          | -1   |       |      | I.    |

| DP DCD current source                 | I <sub>DP_SRC</sub>  |                                          | 7    | 10    | 14   | uA    |

| DM pull-down resistance               | R <sub>DM_DOWN</sub> |                                          | 14.3 | 20    | 24.8 | kΩ    |

| Data detection voltage                | V <sub>DAT_REF</sub> |                                          | 0.25 | 0.325 | 0.4  | V     |

| DP/DM comparator threshold (2.9V)     | V <sub>TH_2P9</sub>  |                                          | 2.8  | 2.9   | 3.0  | V     |

| DP/DM comparator threshold (2.4V)     | V <sub>TH_2P4</sub>  |                                          | 2.3  | 2.4   | 2.5  | V     |

| DP/DM comparator threshold (2.2V)     | V <sub>TH_2P2</sub>  |                                          | 2.1  | 2.2   | 2.3  | V     |

| DP/DM comparator threshold (1.7V)     | V <sub>TH_1V7</sub>  |                                          | 1.6  | 1.7   | 1.8  | V     |

| DP voltage source                     | V <sub>DP_SRC</sub>  |                                          | 0.5  | 0.6   | 0.7  | V     |

| DM voltage source                     | V <sub>DM_SRC</sub>  |                                          | 0.5  | 0.6   | 0.7  | V     |

| DP sink current                       | I <sub>DP_SINK</sub> |                                          | 70   | 100   | 130  | μA    |

| DM sink current                       | I <sub>DM_SINK</sub> |                                          | 70   | 100   | 130  | μA    |

| Leakage current input DP/DM           | I <sub>DP_LKG</sub>  |                                          | -1   |       | +1   | μA    |

| pin                                   | I <sub>DM_LKG</sub>  |                                          | -1   |       | +1   | μA    |

| Logic I/O Pin Characteristics         | (STAT, INT           | r, OTG, /CE, DISC)                       |      |       |      |       |

| Logic low voltage threshold           | V <sub>IL</sub>      |                                          |      |       | 0.4  | V     |

| Logic high voltage threshold          | V <sub>IH</sub>      |                                          | 1.3  |       |      | V     |

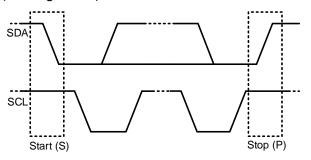

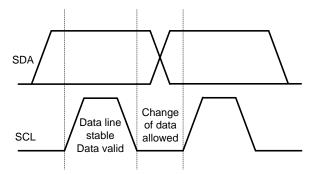

| I <sup>2</sup> C Interface (SDA, SCL) |                      |                                          |      |       |      |       |

| Input high threshold level            | VIH                  | V <sub>PULL_UP</sub> = 1.8V, SDA and SCL | 1.3  |       |      | V     |

| Input low threshold level             | VIL                  | V <sub>PULL_UP</sub> = 1.8V, SDA and SCL |      |       | 0.4  | V     |

| Output low threshold level            | Vol                  | Isink = 5mA                              |      |       | 0.4  | V     |

| I <sup>2</sup> C clock frequency      | f <sub>SCL</sub>     |                                          |      |       | 400  | kHz   |

| Clock Frequency and Watch             | log Timer            | •                                        | •    | •     |      | •     |

| Clock frequency                       | fclk                 |                                          |      | 5     |      | MHz   |

| Watchdog timer                        | twoT                 | REG08h, bits[5:4] = 11                   |      | 160   |      | s     |

© 2023 MPS. All Rights Reserved.

#### TYPICAL PERFORMANCE CHARACTERISTICS

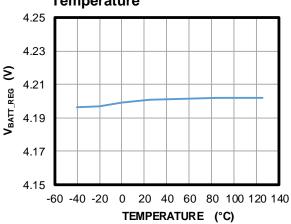

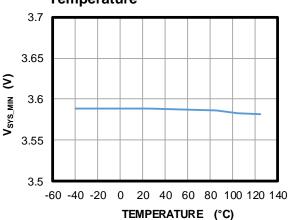

$V_{IN} = 5.0V$ ,  $V_{BATT} =$  full range,  $I^2C$ -controlled,  $I_{CHG} = 1.84A$ ,  $I_{IN\_LIM} = 3.0A$ ,  $V_{IN\_MIN} = 4.3V$ ,  $L = 1.0 \mu H$  (DCR = 14.9m $\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

# Battery Regulation Voltage vs. Temperature

System Minimum Voltage vs. Temperature

Battery Current in Shipping Mode vs. Temperature

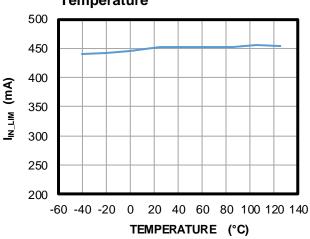

500mA Input Current Limit vs. Temperature

$V_{IN}=5.0V$ ,  $V_{BATT}=$  full range,  $I^2C$ -controlled,  $I_{CHG}=1.84A$ ,  $I_{IN\_LIM}=3.0A$ ,  $V_{IN\_MIN}=4.3V$ ,  $L=1.0\mu H$  (DCR = 14.9m $\Omega$ ),  $T_A=25^{\circ}C$ , unless otherwise noted.

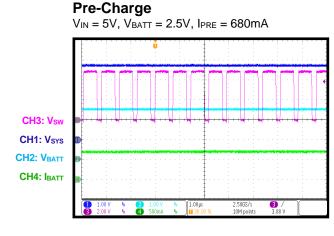

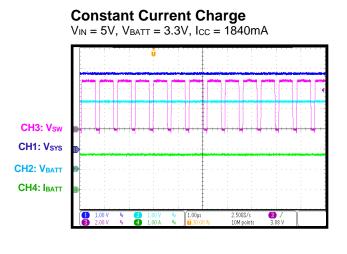

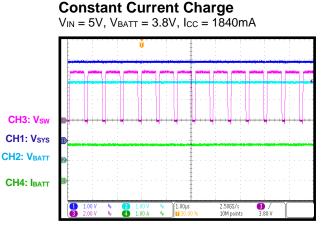

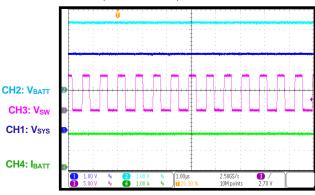

$V_{IN} = 5.0V$ ,  $V_{BATT} = full range$ ,  $I^2C$ -controlled,  $I_{CHG} = 1.84A$ ,  $I_{IN LIM} = 3.0A$ ,  $V_{IN MIN} = 4.3V$ ,  $L = 1.0 \mu H$ (DCR = 14.9m $\Omega$ ), T<sub>A</sub> = 25°C, unless otherwise noted.

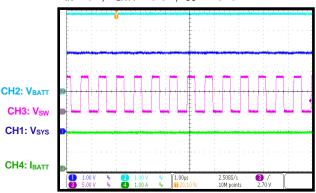

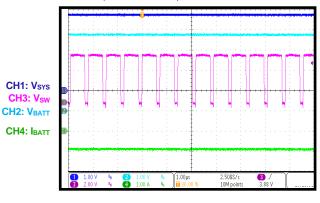

#### **Constant Current Charge**

VIN = 9V, VBATT = 3.3V, ICC = 1840mA

#### **Constant Current Charge**

VIN = 9V, VBATT = 3.8V, ICC = 1840mA

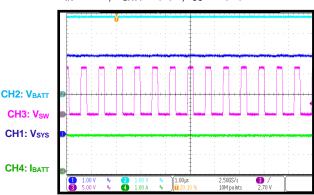

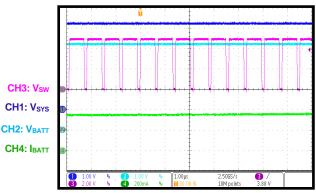

#### **Constant Current Charge**

VIN = 12V, VBATT = 3.3V, ICC = 1840mA

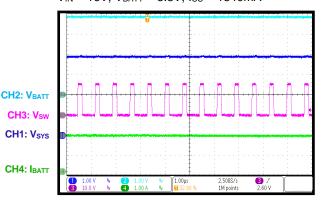

#### **Constant Current Charge**

VIN = 12V, VBATT = 3.8V, ICC = 1840mA

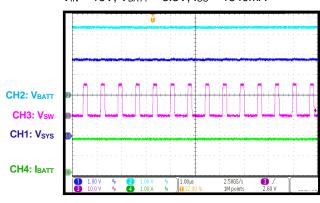

#### **Constant Current Charge**

VIN = 16V, VBATT = 3.3V, ICC = 1840mA

## **Constant Current Charge**

VIN = 16V, VBATT = 3.8V, ICC = 1840mA

$V_{IN} = 5.0V$ ,  $V_{BATT} = \text{full range}$ ,  $I^2C$ -controlled,  $I_{CHG} = 1.84A$ ,  $I_{IN \text{ LIM}} = 3.0A$ ,  $V_{IN \text{ MIN}} = 4.3V$ ,  $L = 1.0 \mu H$ (DCR = 14.9m $\Omega$ ), T<sub>A</sub> = 25°C, unless otherwise noted.

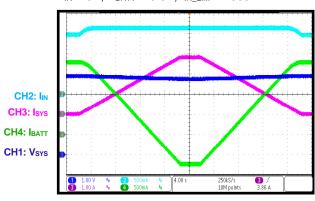

#### **Battery Supplement Mode**

VIN = 5V, VBATT = 3.8V, ISYS = 4.5A

#### **Constant Voltage Charge**

VIN = 5V, VBATT = 4.19V, ISYS = 0A

#### **Input Current Limit**

$V_{IN} = 5V$ ,  $V_{BATT} = 3.8V$ ,  $I_{IN\_LIM} = 1800mA$

#### **Input Voltage Limit**

$V_{IN} = 5V$  (2A),  $V_{BATT} = 3.3V$ ,  $V_{IN\_MIN} = 4.6V$

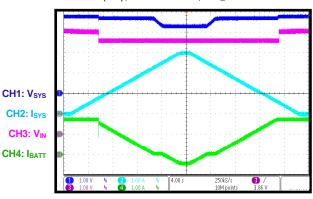

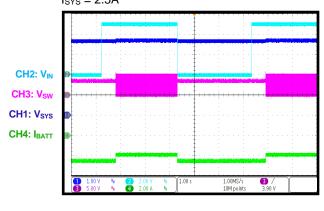

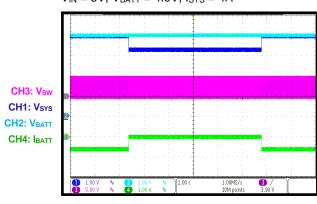

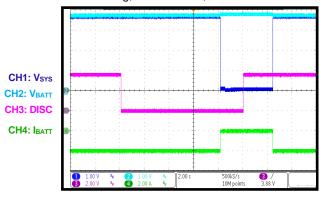

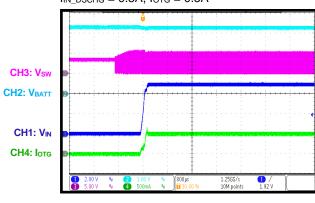

#### Start-Up/Shutdown

$V_{IN} = 5V$ ,  $I_{IN\_LIM} = 500$ mA,  $V_{BATT} = 3.8V$ ,  $I_{SYS} = 2.5A$

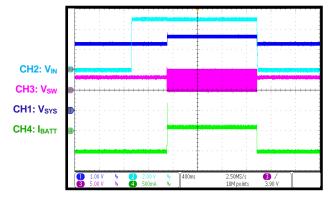

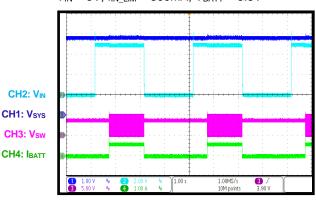

#### Start-Up/Shutdown

$V_{IN} = 5V$ ,  $I_{IN\_LIM} = 500mA$ ,  $V_{BATT} = 3.3V$ ,  $I_{SYS} = 0.5A$

$V_{IN} = 5.0V$ ,  $V_{BATT} =$  full range,  $I^2C$ -controlled,  $I_{CHG} = 1.84A$ ,  $I_{IN\_LIM} = 3.0A$ ,  $V_{IN\_MIN} = 4.3V$ ,  $L = 1.0 \mu H$  (DCR = 14.9m $\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

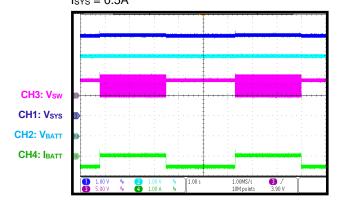

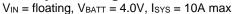

#### **Suspend Mode On/Off**

$V_{IN} = 5V$ ,  $I_{IN\_LIM} = 500$ mA,  $V_{BATT} = 4.0V$ ,  $I_{SYS} = 0.5$ A

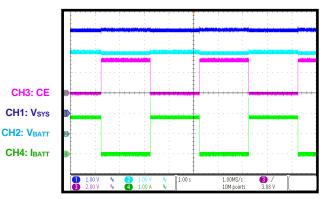

#### Charge On/Off

$V_{IN} = 5V$ ,  $V_{BATT} = 4.0V$ ,  $I_{SYS} = 0A$

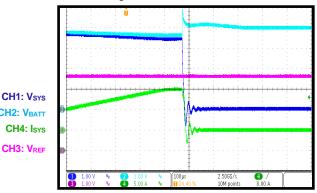

#### **BATTFET On/Off**

$V_{IN} = 5V$ ,  $V_{BATT} = 4.0V$ ,  $I_{SYS} = 4A$

#### VIN Hot Insertion/Removal

$V_{IN} = 5V$ ,  $I_{IN}$  LIM = 500mA,  $V_{BATT} = 3.8V$

#### **SYS Load Transient**

$V_{IN} = 5V$ ,  $V_{BATT} = 3.3V$ , charging disabled,  $I_{SYS} = 1A$  to 3A

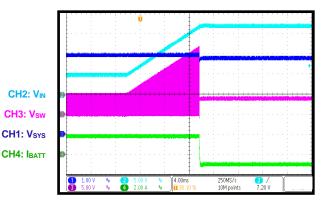

#### **VIN OVP Test**

$V_{\text{IN}} = 5V$  to 17V,  $V_{\text{BATT}} = 3.8V,\,I_{\text{SYS}} = 1A$

CH2: VBATT

CH3: VREF

CH1: V<sub>IN</sub>

CH3: V<sub>SW</sub>

CH3: V<sub>NTC</sub>

CH1: Vsys

CH2: VBATT

CH4: IBATT

CH4: IL

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

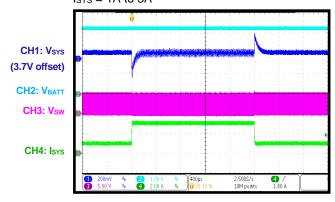

$V_{IN} = 5.0V$ ,  $V_{BATT} = full range$ ,  $I^2C$ -controlled,  $I_{CHG} = 1.84A$ ,  $I_{IN LIM} = 3.0A$ ,  $V_{IN MIN} = 4.3V$ ,  $L = 1.0 \mu H$ (DCR = 14.9m $\Omega$ ), T<sub>A</sub> = 25°C, unless otherwise noted.

#### **Battery Discharge Current**

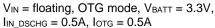

#### **OTG Mode On**

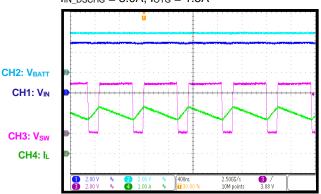

#### **OTG Steady State Operation**

$V_{IN}$  = floating, OTG mode,  $V_{BATT}$  = 4.0V,  $I_{IN\_DSCHG} = 3.0A$ ,  $I_{OTG} = 1.5A$

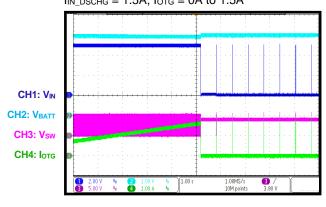

#### **OTG Voltage Regulation**

V<sub>IN</sub> = floating, OTG mode, V<sub>BATT</sub> = 4.0V,  $I_{IN\_DSCHG} = 1.5A$ ,  $I_{OTG} = 0A$  to 1.5A

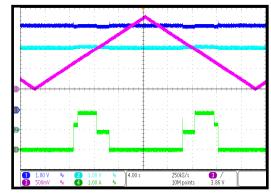

#### **NTC JEITA Operation**

$V_{IN} = 5V$ ,  $V_{BATT} = 4.07V$ ,  $I_{SYS} = 0A$ , JEITA\_ISET = 50%, JEITA\_VSET = -100mV

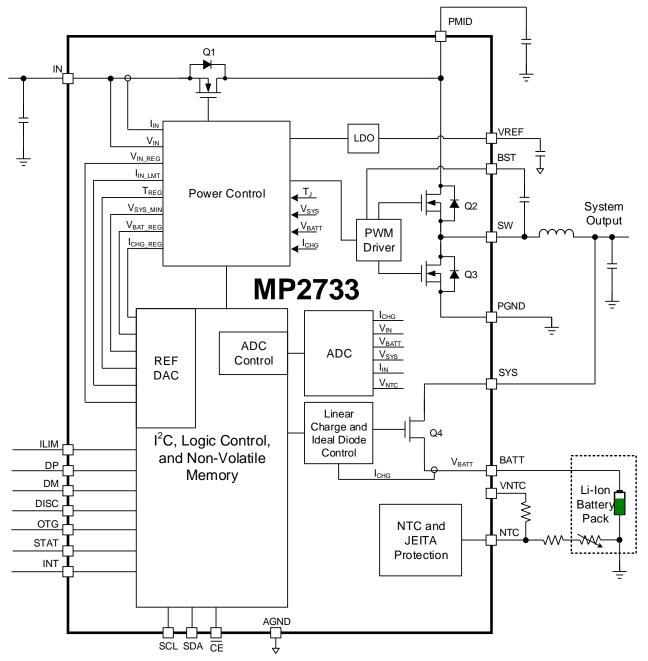

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

#### **OPERATION**

The MP2733 is a highly integrated, 4.5A, switchmode battery charger IC with narrow voltage DC (NVDC) power path management for single-cell Li-ion or Li-polymer battery applications. The device integrates a reverse blocking FET (Q1), a high-side MOSFET (Q2), a low-side MOSFET (Q3), and a battery FET (Q4) between the SYS and BATT pins.

#### **Power Supply**

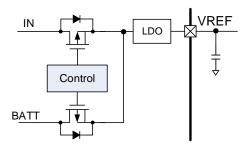

The VREF pin's voltage supplies the internal bias circuits, as well as the high-side MOSFET (HS-FET) and low-side MOSFET (LS-FET) gate drive. The STAT pull-up rail can also be connected to VREF. The VREF pin has an internal LDO with two inputs. One input is from IN, and the other is from a battery. IN and the battery voltage are connected to the input of the LDO via a P-channel MOSFET.

Figure 3 shows the VREF power supply circuit.

Figure 3: VREF Power Supply Circuit

#### **Device Start-Up from Input Source**

When an input source is plugged in, the MP2733 qualifies the input source before start-up. The input source must meet both of the following requirements:

- 1.  $V_{IN} > V_{BATT} + V_{HDRM}$

- 2. VIN LIVLO < VIN < VIN OVIO

If the input power source meets the conditions above, a good input is detected, and the device asserts an INT signal to the host. Then the device detects the input source type via the DP/DM pins. When DP/DM detection completes, the status register bit (VIN\_STAT) changes and an INT pulse is sent to the host. Then the device starts up the step-down converter.

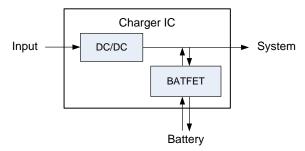

#### **NVDC Power Path Management**

The MP2733 employs an NVDC power structure with the battery FET, decoupling the system

from the battery and thus allowing separate controls between the system and the battery. The system is a priority during start-up, even if the battery is deeply discharged or missing. If the input power is available with a depleted battery. the system voltage is regulated to the minimum system voltage (V<sub>SYS\_REG\_MIN</sub>).

Figure 4 shows the NVDC power structure, which is composed of a front-end, step-down DC/DC converter and a battery FET placed between the SYS and BATT pins.

**Figure 4: NVDC Power Path Management** Structure

The DC/DC converter is a 1.35MHz, step-down switching regulator that directly drives the system load and charges the battery through the battery FET.

The system regulates the voltage in the following ways:

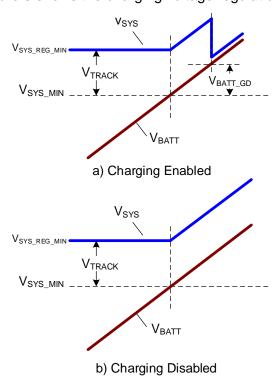

- If the battery voltage (V<sub>BATT</sub>) drops below V<sub>SYS MIN</sub>, the system voltage is regulated at V<sub>SYS REG MIN</sub>, which exceeds V<sub>SYS MIN</sub> by V<sub>TRACK</sub>. The battery FET works linearly to charge the battery via a trickle charge, precharge, or fast charge current, depending on V<sub>BATT</sub>. V<sub>SYS\_MIN</sub> can be set via REG04h, bits[3:1], and V<sub>TRACK</sub> can be set via REG04h, bit[0].

- 2. When  $V_{BATT}$  exceeds  $V_{SYS\_MIN}$  +  $V_{BATT\_GD}$ (60mV), the battery FET fully turns on, and the voltage difference between the system and the battery is the  $V_{DS}$  of the BATTFET. The charge current loop is implemented by the DC/DC converter's PWM control.

- If charging is suspended or completed (the battery FET is off), the system voltage is always regulated at its maximum value (V<sub>SYS MIN</sub>, V<sub>BATT</sub>) + V<sub>TRACK</sub>.

Figure 5 shows the charging voltage regulation.

Figure 5: V<sub>SYS</sub> Variation with V<sub>BATT</sub>

#### **Dynamic Power Management (DPM)**

To meet the maximum current limit in USB specifications and avoid overloading the adapter, the MP2733 features dynamic power management (DPM), and continuously monitors the input current ( $I_{IN}$ ) and input voltage ( $V_{IN}$ ). The total input current limit is configurable to prevent the input source from being overloaded. If the input current increases and reaches the input current limit ( $I_{IN\_LIM}$ ), the charge current is reduced to prioritize the system power.

If the preset  $I_{\text{IN\_LIM}}$  exceeds the adapter's rating, the additional minimum input voltage regulation loop activates to prevent the input power source from being overloaded. When  $V_{\text{IN}}$  falls below the input voltage regulation threshold due to a heavy load, the charge current is reduced to prevent  $V_{\text{IN}}$  from dropping further.

Power path management can operate in two ways:

If V<sub>BATT</sub> < V<sub>SYS\_MIN</sub> + V<sub>BATT\_GD</sub>, the system voltage is regulated at V<sub>SYS\_REG\_MIN</sub>. If the input current reaches I<sub>IN\_LIM</sub>, the input current loop controls the DC/DC converter. If the input voltage drops to V<sub>IN\_MIN</sub>, the input voltage loop controls the converter. Then the

- system voltage drops, and the battery FET driver is pulled down to decrease the charge current. This prioritizes the system power requirement.

- 2. If the battery is directly connected to the system, and  $V_{BATT} > V_{SYS\_MIN} + V_{BATT\_GD}$ , there is a free transition between each control loop. In this circumstance, the charge decreases automatically when  $I_{IN\_LIM}$  or the voltage regulation threshold is reached.

#### **Battery Supplement Mode**

If the device reaches  $I_{\text{IN\_LIM}}$  or the input voltage threshold, the charge current decreases. If the input source is still overloaded when the charge current decreases to zero, the system voltage (V<sub>SYS</sub>) begins to drop. If V<sub>SYS</sub> drops below V<sub>BATT</sub>, the MP2733 enters battery supplement mode, in which the battery simultaneously powers the system and the DC/DC converter.

The MP2733 can operate in ideal diode mode to optimize the control transition between the battery FET and DC/DC converter. The battery FET enters ideal diode mode under either of the following conditions:

- 1. V<sub>IN</sub> starts up from the battery supply system.

- 2.  $V_{BATT} < V_{SYS\_MIN}$ , and  $V_{SYS}$  drops below  $V_{BATT}$ .

During ideal diode mode, the battery FET operates as an ideal diode, and regulates the battery FET's gate drive. The  $V_{DS}$  of the battery FET remains at about 20mV. As the discharge current increases, the battery FET's gate drive increases, and its  $R_{DS}$  decreases until the battery FET is fully on.

#### **Battery Charge Profile**

If  $V_{IN}$  powers on, the CHG\_CONFIG bit = 01, and the CE pin is low, then the device automatically completes a charging cycle without host involvement. However, the host can set different charging parameters to optimize the charge profile by writing to the corresponding registers via the  $I^2C$ .

A new charge cycle starts when all of the following conditions are valid:

- Good input power is inserted

- Battery charging is enabled by the I<sup>2</sup>C, and CE is forced to logic low

- There is no thermistor fault on the NTC pin

- There is no safety timer fault

- The BATTFET is not forced to turn off

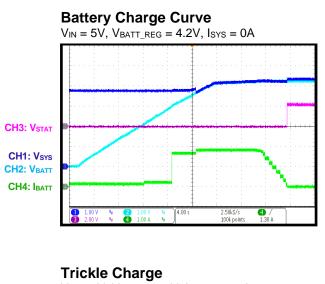

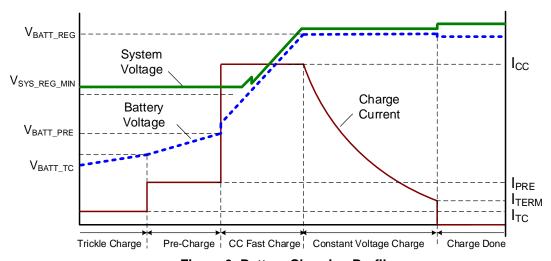

The MP2733 provides four main charging phases: trickle charge, pre-charge, constant current charge, and constant voltage charge. Each phase is described below:

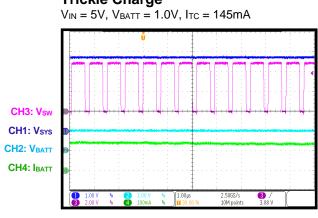

Phase 1 (trickle charge): When the input power qualifies as a good power supply, the MP2733 checks V<sub>BATT</sub> to determine whether trickle charge is required. If V<sub>BATT</sub> is below V<sub>BATT\_TC</sub> (2.0V), a trickle-charge current is applied on the battery, which helps reset the protection circuit in the battery pack. The trickle-charge current can be set via REG06h, bit[4]. If REG06h, bit[4] is set to 1, the trickle-charge current is 185mA. If REG06h, bit[4] is set to 0, the trickle-charge current is 145mA.

Phase 2 (pre-charge): If V<sub>BATT</sub> exceeds V<sub>BATT\_TC</sub>, the MP2733 starts to safely pre-charge the depleted battery until V<sub>BATT</sub> reaches the pre-charge to fast charge threshold (V<sub>BATT\_PRE</sub>). If V<sub>BATT\_PRE</sub> is not reached before the pre-charge timer (1hr) expires, the charge cycle ends and a corresponding timeout fault signal is asserted. The pre-charge current can be configured via the I<sup>2</sup>C register REG06h, bits[7:4], and can be set between 150mA and 750mA.

Phase 3 (constant current charge): If V<sub>BATT</sub> exceeds V<sub>BATT\_PRE</sub> set via REG05h, bit[7], the MP2733 enters a constant current charge (fast charge) phase. The fast charge current can be configured up to 3A via REG05h, bits[5:0].

There are two stages of fast charge. First, the battery FET works linearly to charge the battery with a fast charge current. Once  $V_{BATT}$  exceeds  $V_{SYS\_MIN} + V_{BATT\_GD}$ , the battery FET fully turns on. The charge current loop is implemented by the PWM control of the buck converter.

Phase 4 (constant voltage charge): When V<sub>BATT</sub> reaches the configurable float voltage (V<sub>BATT\_REG</sub>) set via REG07h, bits[7:1], the charge current begins to taper off.

The charge cycle is considered complete when the charge current reaches the battery termination threshold (I<sub>TERM</sub>) set via REG06h, bits[3:0] after a 200ms termination deglitch time (assuming that the termination function is enabled if REG08h, bit[7] is set to 1). If I<sub>TERM</sub> is not reached before the safety charge timer expires (see the Safety Timer section on page 24), the charge cycle ends, and a corresponding timeout fault signal is asserted.

Figure 6 shows the charging profile.

Figure 6: Battery Charging Profile

During the charging process, the actual charge current may be less than the register setting due to other loop regulations, such as DPM regulation (input current limit or input voltage regulation loop) or thermal regulation. Thermal regulation reduces the charge current such that the IC junction temperature does not exceed the preset limit. Multiple thermal regulation thresholds (between 60°C and 120°C) help the system design meet the thermal requirements for different applications. The junction temperature regulation threshold can be set via REG02h, bits[3:2].

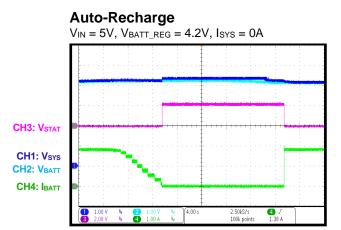

#### **Auto-Recharge**

When the battery is done charging, the battery may be discharged due to system consumption or self-discharge. When  $V_{BATT}$  is discharged below the recharge threshold after a 200ms auto-recharge deglitch time, the MP2733 automatically begins another charging cycle.

#### **CE Control**

CE is a logic input pin that enables and disables battery charging, or starts a new charging cycle. Battery charging is enabled when CHG\_CONFIG (REG04h, bits[5:4]) is set to 01 and the CE pin is pulled to a low logic.

#### **Battery Over-Voltage Protection (OVP)**

The MP2733 is designed with built-in battery over-voltage protection (OVP). If  $V_{BATT}$  exceeds 103.5% of  $V_{BATT\_REG}$ , the MP2733 immediately suspends charging and asserts a fault. If battery OVP occurs, charging is disabled but the DC/DC converter continues operating.

#### System Over-Voltage Protection (OVP)

The MP2733 monitors the voltage at the SYS pin. If an over-voltage condition ( $V_{SYS} > V_{BATT\_REG} + 0.4V$ ) is detected, the DC/DC converter turns off, and the system is powered by the battery via the battery FET.

#### **Automatic Input Current Optimizer (AICO)**

The device provides an optimized input current limit ( $I_{\text{IN\_LIM}}$ ) without overloading the input source. This function can be enabled or disabled by configuring the AICO\_EN bit (disabled by default). If AICO is enabled, automatic input current optimization (AICO) is triggered when  $I_{\text{IN\_LIM}}$  is set to a larger current, and  $V_{\text{IN}}$  drops to  $V_{\text{IN\_MIN}}$ . This function decreases  $I_{\text{IN\_LIM}}$  step by

step until  $V_{\text{IN}}$  exits  $V_{\text{IN\_MIN}}$  control.  $I_{\text{IN\_LIM}}$  remains optimized and does not automatically run the AICO function unless another  $V_{\text{IN\_MIN}}$  event occurs.

The actual  $I_{\text{IN\_LIM}}$  is reported in the  $I_{\text{IN\_DPM}}$  register when the AICO function is enabled (AICO\_EN = 1). If the AICO function is disabled (AICO\_EN = 0),  $I_{\text{IN\_LIM}}$  is set by the IIN\_LIM register. Any write to IIN\_LIM can reset  $I_{\text{IN\_DPM}}$  to the same  $I_{\text{IN\_LIM}}$  value as when the AICO function is enabled.

#### **Input Source Type Detection**

The MP2733 features input source detection compatible with USB Battery Charging Specification 1.2 (BC1.2) and nonstandard adapters. The user can force DP/DM detection in host mode by writing 1 to USB\_DET\_EN (REG0Bh, bit[5]).

When  $V_{\text{IN}}$  is first applied and a good input source is detected, BC1.2 detection begins with data content detection (DCD). If DCD is effective, the standard downstream port (SDP), charging downstream port (CDP), and dedicated charging port (DCP) can be distinguished. If the 500ms DCD timer expires, then the MP2733 proceeds with nonstandard adapter detection.

DCD uses a current source to detect when the data pins have made contact during an attachment event. The protocol for DCD is described below:

- 1. The portable device (PD) detects  $V_{\text{IN}}$  assertion.

- The PD turns on DP (I<sub>DP\_SRC</sub>) and the DM pull-down resistor.

- 3. The PD waits for the DP line to pull low.

- 4. If the DP line is detected to be low for 10ms, the PD starts primary detection.

- If data contact is not detected, the DCD timer (about 500ms) expires.

After the DCD timer expires, the PD turns off  $I_{DP\_SRC}$  and the DM pull-down resistor. Then the 50ms timer starts, and the PD can detect a special adapter. If a special adapter is detected, an INT signal is sent to the host. Otherwise, the PD starts primary detection after the 50ms timer expires.

Primary detection is used to distinguish between USB hosts (or the SDP) and different types of charging ports. During primary detection, the IC turns on  $V_{DP\_SRC}$  on DP, and  $I_{DM\_SINK}$  on DM. If the portable device is attached to a USB host, the DM pin pulls low. The SDP is detected, and an INT signal is sent to the host.

If the DM pin is high, the IC goes into secondary detection, which distinguishes between a CDP and a DCP.

During secondary detection, the IC turns on  $V_{\text{DM\_SRC}}$  on DM, and  $I_{\text{DP\_SINK}}$  on DP. If the input source is a CDP port and DP is low, then the CDP is detected, and an INT signal is sent to the host.

If DP is high, the DCP source is detected, and an INT signal is sent to the host. In this case, after turning off  $V_{DM\_SRC}$  and  $I_{DP\_SINK}$ ,  $V_{DP\_SRC}$  is applied to DP, and the IC goes to fast charge detection.

Fast charge detection identifies whether the input source has fast charge capability.

If DM is always high during fast charge detection, the input source has no fast charge capability. If DM is low for 40ms when the input source has fast charge capability, the MP2733 sends an INT signal to the host. The MP2733 features an I<sup>2</sup>C-configurable DP/DM output for host-controlled communication, with various fast charge protocols.

Table 1 lists input current limits that are compatible with USB specifications and BC1.2.

Table 1: Input Current Limit vs. USB Type

| DP/DM<br>Detection         | I <sub>IN_LIM</sub> (A) | V <sub>IN_OVP</sub> (7) (V) | V <sub>IN_MIN</sub> (V) |

|----------------------------|-------------------------|-----------------------------|-------------------------|

| Nonstandard adapter (1A)   | 1                       | 6                           | 3.7 to 5.2              |

| Nonstandard adapter (2.1A) | 2.1                     | 6                           | 3.7 to 5.2              |

| Nonstandard adapter (2.4A) | 2.4                     | 6                           | 3.7 to 5.2              |

| SDP                        | 0.5                     | 6                           | 3.7 to 5.2              |

| CDP                        | 1.5                     | 6                           | 3.7 to 5.2              |

| DCP                        | 1.8                     | 6                           | 3.7 to 5.2              |

#### Note:

USB detection is independent of the charge enable status. After DP/DM detection completes, the MP2733 indicates the USB port type in the status register VIN\_STAT (REG0Ch, bits[7:5]) and fast charge adapter (REG17h, bit[6]), then asserts an INT signal to the host. The host can revise the input current limit according to detection results.

#### Input Current Limit Setting via ILIM

For safe operation, the MP2733 has an additional hardware pin (ILIM) to adjust the maximum input current limit. The limit can be set by connecting a resistor from ILIM to GND. The actual input current limit is the lower value between what is set by the ILIM pin and the value set by the I<sup>2</sup>C.

The input current limit set by the ILIM pin can be calculated with Equation (1):

$$I_{IN\_LIM} = \frac{120}{R_{ILIM}(k\Omega)}(A)$$

(1)

#### **Battery Temperature Monitor in Charge Mode**

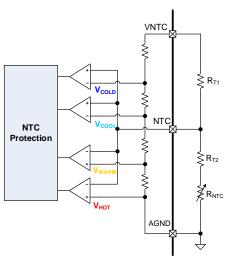

The MP2733 continuously monitors the battery's temperature by measuring the voltage at the NTC pin. This value is typically determined by a negative temperature coefficient (NTC) thermistor and external voltage dividers. For the NTC thermistor, a hotter ambient temperature corresponds with a lower resistance and voltage ratio, and vice versa.

Figure 7 on page 24 shows an NTC protection circuit. The external resistor dividers and the internal reference resistor series are pulled up to the VNTC pin. The voltage ratios between the internal and external dividers are compared to determine whether an NTC protection has been triggered. The VNTC voltage (1.7V) is regulated by an LDO that is powered from VREF. The VNTC pin is available in both charge mode and On-the-Go (OTG) mode.

<sup>7)</sup>  $V_{IN_{OVP}}$  can only be selected by the OTP via REG18h.

**Figure 7: NTC Protection Circuit**

The MP2733 provides standard and JEITA battery temperature monitoring, which can be selected via the NTC\_TYPE bit. If the standard type is selected, and the external voltage ratio transitions from the high temperature threshold ( $V_{\text{HOT}}$ ) to the low temperature threshold ( $V_{\text{COLD}}$ ), this means that the battery temperature is out of the cold-to-hot range. The IC suspends charging and reports the NTC fault. Once the battery temperature is within the cold-to-hot temperature range again, charging resumes automatically.

If the JEITA type is selected, the MP2733 monitors four temperature thresholds:

- 1) Cold temperature threshold ( $T_{NTC}$  < 0°C, default)

- 2) Cool temperature threshold (0°C <  $T_{NTC}$  < 15°C, default)

- 3) Warm temperature threshold (45°C < T<sub>NTC</sub> < 55°C, default)

- 4) Hot temperature threshold ( $T_{NTC} > 55$ °C, default)

For a given NTC thermistor, these temperatures correspond to the values for  $V_{\text{COLD}}$ ,  $V_{\text{COOL}}$ ,  $V_{\text{WARM}}$ , and  $V_{\text{HOT}}$ , respectively. These voltage thresholds can be configured via REG16h, bits[5:0] to set different temperature ranges.

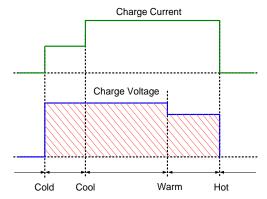

If  $V_{NTC} < V_{HOT}$  or  $V_{NTC} > V_{COLD}$ , charging and timers are suspended. If  $V_{HOT} < V_{NTC} < V_{WARM}$ , then  $V_{BATT\_REG}$  is reduced by 200mV (configured via REG16h, bit[7]). If  $V_{COOL} < V_{NTC} < V_{COLD}$ , the charging current is reduced to 16.7% of its set value, which can be configured via REG16h, bit[6]. Figure 8 shows the NTC window with JEITA control.

Figure 8: NTC Window with JEITA Control

The MP2733 provides PCB over-temperature (OT) monitoring. The PCB OT response is selected by the NTC\_OPTION bit (REG02h, bit[1]). If this bit is set to 1, PCB over-temperature protection (OTP) is enabled. If this bit is set to 0 (the default setting), the battery temperature monitoring and corresponding protection features described above are utilized instead.

While monitoring OT conditions in the PCB, the IC continuously monitors the PCB temperature at the NTC pin. If the NTC pin's voltage is below the threshold that uses  $V_{HOT}$ , the DC/DC converter and battery FET turn off. Operation resumes once the NTC pin voltage returns to its normal value.

If the NTC thermistor is removed, NTC is pulled up to VNTC (see Figure 7). If the NTC voltage exceeds 95% of VNTC, then the NTC thermistor is detected to be floating. The MP2733 sends an INT signal to the host, and the RNTC FLOAT STAT bit is set to 1.

# Battery Temperature Monitor in On-the-Go (OTG) Boost Mode

In boost mode, the device monitors whether the battery temperature is within the  $V_{\text{COLD}}$  and  $V_{\text{HOT}}$  thresholds, unless boost mode temperature monitoring is disabled by setting EN\_OTG NTC (REG02h, bit[5]) to 0. If the temperature goes outside of these thresholds, boost mode is suspended. Once the temperature returns to within these thresholds, boost mode resumes.

#### **Charging STAT Indication**

The MP2733 indicates the charging state on the open-drain STAT pin. Table 2 shows the STAT

status. The STAT pin function can be disabled by setting the STAT\_EN bit to 0.

**Table 2: Operation Indications**

| STAT               | Charging State                                                                     |

|--------------------|------------------------------------------------------------------------------------|

| Low                | Charging                                                                           |

| High               | Charging complete, charge disabled, input OVP, battery discharge standby mode      |

| Blinking at<br>1Hz | Charging suspended (battery OVP, system OVP, timer fault, NTC fault, or NTC float) |

#### Interrupt to Host (INT)

The MP2733 also has an alert mechanism that can output an interrupt signal via the INT pin to notify the system of updates by outputting a 256µs, low-state INT pulse. Events that can trigger an INT output are listed below:

- Good input source detected

- DP/DM USB detection completed

- Input removed

- Charge completed

- NTC floats

- VINPPM or IINPPM has been reached

- Any fault in REG0Dh (watchdog timer fault, OTG fault, thermal shutdown, safety timer fault, battery OVP fault, NTC fault) has occurred

If a fault occurs, the charger sends out an INT signal. The fault status is not latched, meaning that the fault status is cleared when the fault condition is removed.

#### **Safety Timer**

The MP2733 provides both a pre-charge and complete charge safety timer to prevent extended charging cycles due to abnormal battery conditions. The total safety timer for both trickle charge and pre-charge is 1 hour when VBATT is below VBATT\_PRE. The complete charge safety timer starts when the battery enters constant current charge. The user can configure the constant current charge safety timer via CHG\_TMR (REG08h, bits[2:1]). If the safety timer function is not used, it can be disabled by EN\_TIMER (REG08h, bits[0]) while initializing charger configuration.

The safety timer is reset at the beginning of a new charging cycle. Before the safety timer expires, any of the actions listed below can reset the safety timer:

- A new charge cycle begins by either input insertion or automatic recharge

- Toggling the CE pin low, high, then low (charging enabled)

- Writing CHG\_CONFIG (REG04h, bits[5:4]) from 00 to 01 (charging enabled)

- Writing EN\_TIMER (REG08h, bit[0]) from 0 to 1 (safety timer enabled)

When safety timer expires, the safety timer fault bit (REG17h, bit[7]) is set to 1 and INT is asserted to the host. Writing the BG\_EN bit (REG09h, bit[3]) from 1 to 0 (or re-inserting the input) re-enables input detection, clears the safety timer fault, and restarts the safety timer.

The MP2733 automatically adjusts or suspends the timer if any fault occurs. The timer is suspended if any of the following conditions are met:

- The battery enters supplement mode and  $V_{\text{BATT}} < V_{\text{SYS\_MIN}}$

- Battery OVP occurs

- An NTC hot or cold fault occurs

- The NTC pin is floating

- 0 is written to EN\_TIMER (REG08h, bit[0])

The MP2733 provides a way to double the remaining time left on the timer, which is enabled by the TMR2X\_EN bit. If the input current limit, input voltage regulation, or thermal regulation threshold is reached, the remaining time on the timer is doubled when TMR2X\_EN is enabled. Once the device is cleared of the conditions listed above, the remaining time returns to the original setting.

The safety timer does not operate in USB Onthe-Go (OTG) mode.

#### **Watchdog Timer**

The MP2733 is a host-controlled device, but it can operate in a default mode without host control. In default mode, all registers are set to the default settings, and the WATCHDOG\_FAULT command is set to 1.

In host-controlled mode, all the parameters can be configured by the host. To keep the device in host mode, the host has to periodically reset the watchdog timer by setting the WATCHDOG TIMER RESET bit (REG08h, bit[3]) to 1 before the watchdog timer expires. If the watchdog timer expires, some of the registers are reset to their default values. See the I<sup>2</sup>C Register Map on page 29 to determine which registers are reset after the watchdog timer expires.

The following actions reset the watchdog timer and ensure that the IC recovers from a watchdog timer fault:

- Writing 1 to the WATCHDOG\_TIMER\_RESET bit (REG08h, bit[3])

- Toggling the WATCHDOG TIMER ENABLE bit (disable first, then enable)

#### Thermal Regulation and Thermal Shutdown

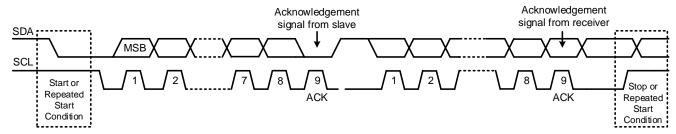

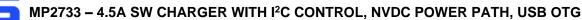

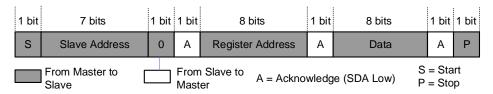

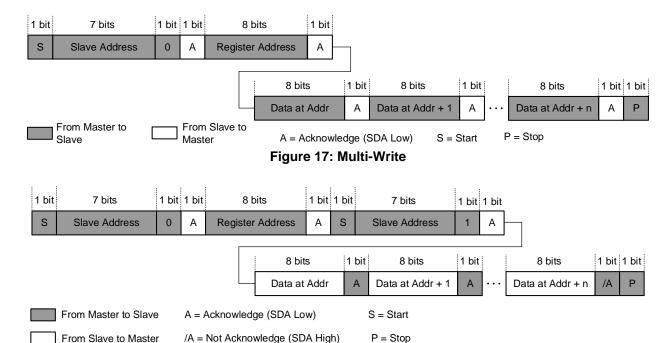

The MP2733 continuously monitors the internal junction temperature to maximize power delivery and avoid overheating the chip. If the internal junction temperature reaches the thermal regulation threshold (set by the TJ\_REG bits), the MP2733 starts to reduce the charge current to prevent higher power dissipation. During thermal regulation, the THERM STAT bit is set to 1.