## **MP5479**

## 2.7V to 5.5V PMIC with Four 2A/2.5A/4.5A/4.5A Buck Converters, 5 LDOs, and Configurable System Settings via I<sup>2</sup>C and MTP

#### **DESCRIPTION**

The MP5479 is a complete power management solution that integrates four high-efficiency step-down DC/DC converters, five low-dropout regulators, and a flexible logic interface.

Constant-on-time (COT) control in the DC/DC converter provides fast transient response. The adjustable switching frequency (up to 2.75MHz) during CCM greatly reduces the external inductor and capacitor value. Full protection features include UVLO, OCP, OVP, and thermal shutdown.

The output voltage is adjustable through the I<sup>2</sup>C bus or preset by the MTP (multiple-time programmable) interface. The power-on/off sequence is also programmable via the MTP and can be controlled through I<sup>2</sup>C bus online.

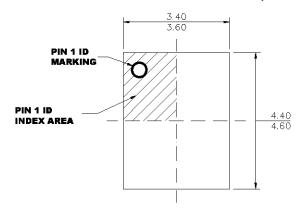

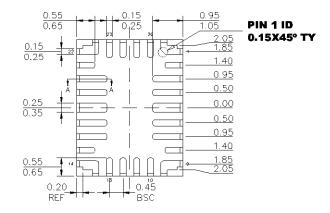

The MP5479 requires a minimal number of external components, and is available in a space-saving QFN-26 (3.5mmx4.5mm) package with wettable flanks.

#### **FEATURES**

#### High-Efficiency Step-Down Converters:

- Buck 1: 4.5A DC/DC Converter

- Buck 2: 2.5A DC/DC Converter

- Buck 3: 4.5A DC/DC Converter

- Buck 4: 2A DC/DC Converter

- Buck 1 and Buck 3 Can Work in Parallel

- Buck 2 and Buck 4 Can Work in Parallel

- 2.7V to 5.5V Operating Input Range

- 0.4V to 3.58V/12.5mV Step or 0.4V to 2.2V/7.4mV Step Optional V<sub>OUT</sub> Range for Buck 1, Buck 2, and Buck 3

- 0.4V to 3.58V/12.5mV Step V<sub>OUT</sub> Range for Buck 4

- Adjustable Switching Frequency

- o Adjustable Soft-Start Time

- Adjustable Phase Delay

- Programmable Forced PWM, Auto-PFM, PWM Mode

- Output OCP, OVP

#### Low-Dropout Regulators:

- One Dedicated RTC LDO

- Four Low-Noise LDOs

- Two Separate Input Power Supplies

o 50mV Dropout at 300mA Load

#### • System:

- o I<sup>2</sup>C Bus and User-Programmable MTP

- Two-Time Programmable MTP (1)

- Power-On/Off Control

- Multi-Function LDO2/EN1 Pin (EN1 Input Logic Level ≤ 3.3V)

- o Power-On Reset Output

- Flexible Power-On/Off Sequence via MTP (0.5ms/2ms/8ms/16ms Selectable Time Slot)

- Flexible DC/DC, LDO On/Off via the MTP

- Available in a QFN-26 (3.5mmx4.5mm)

Package

Optimized Performance with MPS Inductor MPL-AL6050 Series

#### Note:

The two-time programmable MTP is only for the standard version of the MP5479GRM-0000.

## **APPLICATIONS**

- Infotainment

- Video Recorders

- Display Electronics

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

8/26/2021

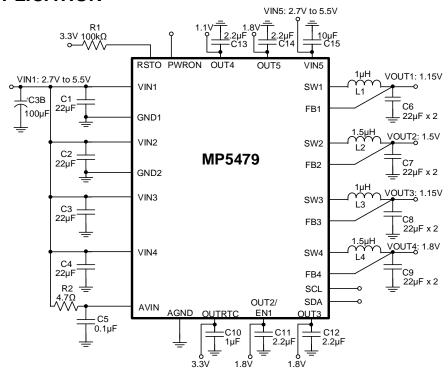

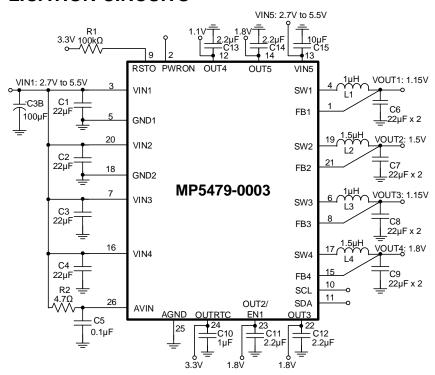

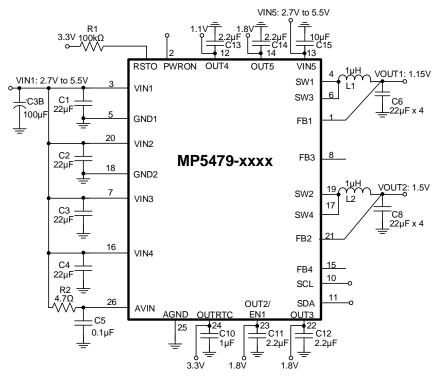

## TYPICAL APPLICATION

## MTP E-FUSE SELECTED TABLE BY DEFAULT (MP5479GRM-0003):

|                                |        |        |        |        | -            |       |       |           |       |

|--------------------------------|--------|--------|--------|--------|--------------|-------|-------|-----------|-------|

| MTP Items                      | Buck 1 | Buck 2 | Buck 3 | Buck 4 | LDORTC       | LDO2  | LDO3  | LDO4      | LDO5  |

| Output voltage                 | 1.15V  | 1.5V   | 1.15V  | 1.8V   | 3.3V         | 1.8V  | 1.8V  | 1.1V      | 1.8V  |

| Initial on/off                 | On     | On     | On     | On     | On           | On    | On    | On        | On    |

| Mode                           | FPWM   | FPWM   | FPWM   | FPWM   |              |       | N/A   |           |       |

| Power-on delay                 | 0ms    | 4.5ms  | 0ms    | 4.5ms  | Always<br>on | 5.5ms | 5.5ms | 5.5m<br>s | 9.5ms |

| Soft-start time                | 300µs  | 300µs  | 300µs  | 300µs  |              |       | N/A   |           |       |

| Switching frequency            |        |        |        | 2      | .2MHz        |       |       |           |       |

| PWRON MODE                     |        |        |        | 0 (lev | el trigger)  |       |       |           |       |

| RSTODELAY                      |        |        |        | ;      | 50ms         |       |       |           |       |

| Buck 1 peak current limit      |        |        |        |        | 9.3A         |       |       |           |       |

| Buck 2 peak current limit      |        |        |        |        | 6.1A         |       |       |           |       |

| Buck 3 peak current limit      |        |        |        |        | 9.3A         |       |       |           |       |

| Buck 4 peak current limit      |        | 6.1A   |        |        |              |       |       |           |       |

| I <sup>2</sup> C slave address |        | ·      | ·      | ·      | 0x69         |       |       | ·         |       |

| MTP configure code             |        |        |        |        | 0003         |       |       |           |       |

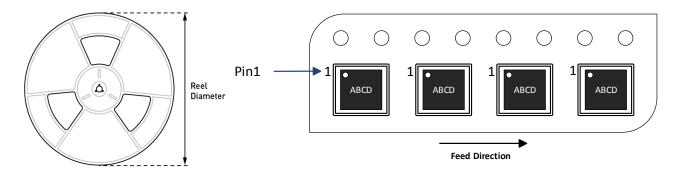

#### ORDERING INFORMATION

| Part Number*     | Package              | Top Marking | MSL Rating |

|------------------|----------------------|-------------|------------|

| MP5479GRM-xxxx** | QFN-26 (3.5mmx4.5mm) | See Below   | 4          |

| MP5479GRM-0003   | QFN-26 (3.5mmx4.5mm) | See Below   | I          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP5479GRM-xxxx-Z).

#### **TOP MARKING**

**MPSYW**

M5479

LLLLL

MPS: MPS prefix Y: Year code W: Week code M5479: Part number LLLLL: Lot number

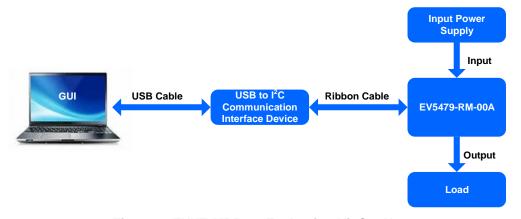

### **EVALUATION KIT EVKT-MP5479**

EVKT-MP5479 kit contents (items below can be ordered separately):

| # | Part Number    | Item                                                                                                     | Quantity |

|---|----------------|----------------------------------------------------------------------------------------------------------|----------|

| 1 | EV5479-RM-00A  | MP5479GRM evaluation board                                                                               | 1        |

| 2 | EVKT-USBI2C-02 | Includes one USB to I <sup>2</sup> C communication interface device, one USB cable, and one ribbon cable | 1        |

| 3 | MP5479-0000    | MP5479 IC, which can be used for MTP programming                                                         | 2        |

#### Order direct from MonolithicPower.com or our distributors.

Figure 1: EVKT-MP5479 Evaluation Kit Set-Up

<sup>\*\* &</sup>quot;xxxx" is the configuration code identifier for the register setting stored in the MTP. The default number is "0003". Each "x" can be a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number, even if ordering the "0003" code. MP5479GRM-0003 is the default version, which can be written to the MTP one time. MP5479GRM-0000 is the standard version for sampling, which can be written to the MTP two times.

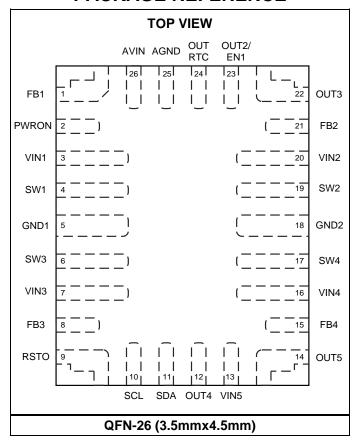

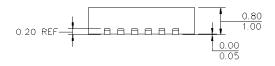

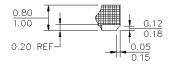

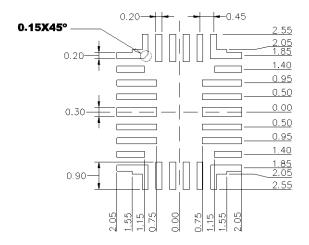

## **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                                                                                                                                                     |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | FB1   | Feedback of buck 1. Connect buck 1's output directly to this pin.                                                                                                                                                                                               |

| 2     | PWRON | <b>Power-on/off input.</b> Logic input pin to start up or shut down the device. This pin should be pulled high by an external voltage.                                                                                                                          |

| 3     | VIN1  | <b>Buck 1 supply voltage input.</b> The MP5479 operates from a 2.7V to 5.5V input rail. It requires a ceramic capacitor to decouple the input rail. Connect using a wide PCB trace. VIN1, VIN2, VIN3, VIN4, and AVIN must be connected to the same bus voltage. |

| 4     | SW1   | Buck 1 switch output. Connect using a wide PCB trace.                                                                                                                                                                                                           |

| 5     | GND1  | <b>Buck 1 and buck 3 power ground.</b> Requires special consideration during PCB layout. Connect to GND with copper traces and vias.                                                                                                                            |

| 6     | SW3   | Buck 3 switch output. Connect using a wide PCB trace.                                                                                                                                                                                                           |

| 7     | VIN3  | <b>Buck 3 supply voltage input.</b> The MP5479 operates from a 2.7V to 5.5V input rail. It requires a ceramic capacitor to decouple the input rail. Connect using a wide PCB trace. VIN1, VIN2, VIN3, VIN4, and AVIN must be connected to the same bus voltage. |

| 8     | FB3   | Buck 3 feedback. Connect buck 3's output directly to this pin.                                                                                                                                                                                                  |

| 9     | RSTO  | <b>Reset output from the PMIC to CPU.</b> Open-drain output. This pin requires an external pullup resistor.                                                                                                                                                     |

| 10    | SCL   | I <sup>2</sup> C clock signal input.                                                                                                                                                                                                                            |

| 11    | SDA   | I <sup>2</sup> C data pin.                                                                                                                                                                                                                                      |

## PIN FUNCTIONS (continued)

| Pin # | Name     | Description                                                                                                                                                                                                                                                                             |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | OUT4     | LDO4 output. LDO4 is powered by VIN5.                                                                                                                                                                                                                                                   |

| 13    | VIN5     | <b>LDO4 and LDO5 power input pin.</b> This pin operates from a 2.7V to 5.5V input voltage. Connect VIN5 to VIN1 if LDO4 and LDO5 are not used.                                                                                                                                          |

| 14    | OUT5     | LDO5 output. LDO5 is powered by VIN5.                                                                                                                                                                                                                                                   |

| 15    | FB4      | Buck 4 feedback. Connect buck 4's output directly to this pin.                                                                                                                                                                                                                          |

| 16    | VIN4     | <b>Buck 4 supply voltage input.</b> The MP5479 operates from a 2.7V to 5.5V input rail. It requires a ceramic capacitor to decouple the input rail. Connect using a wide PCB trace. VIN1, VIN2, VIN3, VIN4, and AVIN must be connected to the same bus voltage.                         |

| 17    | SW4      | Buck 4 switch output. Connect using a wide PCB trace.                                                                                                                                                                                                                                   |

| 18    | GND2     | <b>Buck 2 and buck 4 power ground.</b> This pin requires special consideration during PCB layout. Connect to GND with copper traces and vias.                                                                                                                                           |

| 19    | SW2      | Buck 2 switch output. Connect using a wide PCB trace.                                                                                                                                                                                                                                   |

| 20    | VIN2     | <b>Buck 2, LDORTC, LDO2, and LDO3 supply voltage input.</b> The MP5479 operates from a 2.7V to 5.5V input rail. It requires a ceramic capacitor to decouple the input rail. Connect using a wide PCB trace. VIN1, VIN2, VIN3, VIN4, and AVIN must be connected to the same bus voltage. |

| 21    | FB2      | Buck 2 feedback. Connect buck 2's output directly to this pin.                                                                                                                                                                                                                          |

| 22    | OUT3     | LDO3 output. LDO3 is powered by VIN2.                                                                                                                                                                                                                                                   |

| 23    | OUT2/EN1 | <b>LDO2 output or EN1.</b> LDO2 is powered by VIN2. When configuring this pin as EN1, it acts as an input pin. Pull EN1 up or down to enable or disable the MP5479, respectively.                                                                                                       |

| 24    | OUTRTC   | RTC LDO output. This LDO is powered by VIN2.                                                                                                                                                                                                                                            |

| 25    | AGND     | Analog ground. Connect this pin to GND1 and GND2.                                                                                                                                                                                                                                       |

| 26    | AVIN     | <b>Power supply input for logic circuitry.</b> Bypass this pin with a $0.1\mu F$ ceramic capacitor to AGND. Connect AVIN to the system input through a $4.7\Omega$ resistor. VIN1, VIN2, VIN3, VIN4, and AVIN must be connected to the same bus voltage.                                |

### ABSOLUTE MAXIMUM RATINGS (2)

| Thermal Resistance      | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |

|-------------------------|-----------------------|-----------------------|

| QFN-26 (3.5mmx4.5mm)    |                       |                       |

| EV5479-RM-00A (7)       | 20                    | 5 °C/W                |

| JESD51-7 <sup>(8)</sup> | 44                    | 9 °C/W                |

#### Notes:

- Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{\text{JA}}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = (TJ (MAX) - T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation may lead to excessive die temperature, and the regulator can go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- HBM, per JEDEC specification JESD22-A114; CDM, per JEDEC specification JESD22-C101. JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

- The device is not guaranteed to function outside of its operating conditions.

- Operating devices at junction temperatures greater than 125°C is possible; contact MPS for details.

- Measured on EV5479-RM-00A, 4-layer PCB.

- Measured on JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

6

## **ELECTRICAL CHARACTERISTICS**

$V_{IN1} = V_{IN2} = V_{IN3} = V_{IN4} = V_{IN5} = AVIN = 5V, T_J = -40^{\circ}C \ to \ +125^{\circ}C^{\ (9)}, typical \ value \ is tested \ at \ T_J = 25^{\circ}C, unless \ otherwise \ noted.$

| Parameter                                | rameter Symbol Condition |                                                                         |       | Тур  | Max   | Units    |

|------------------------------------------|--------------------------|-------------------------------------------------------------------------|-------|------|-------|----------|

| Supply current (no switching)            | l <sub>IN</sub>          | No switching, feedback is high, T <sub>J</sub> = 25°C                   |       | 300  | 600   | μΑ       |

| Shutdown current                         | lu, ozo                  | All regulators disabled except LDORTC, T <sub>J</sub> = 25°C            |       | 30   | 60    | μA       |

| Shalaowh current                         | I <sub>IN_STD</sub>      | All regulators disabled except LDORTC, T <sub>J</sub> = -40°C to +125°C |       | 30   | 120   | μΑ       |

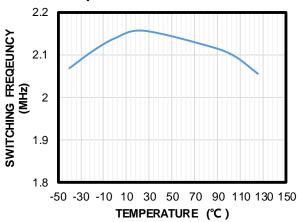

| Default oscillation frequency            | fsw                      |                                                                         | 1.8   | 2.2  | 2.4   | MHz      |

| Thermal shutdown entry threshold (11)    | T <sub>OTP_R</sub>       |                                                                         |       | 153  |       | °C       |

| Thermal shutdown recovery threshold (11) | T <sub>HYS</sub>         |                                                                         |       | 130  |       | °C       |

| Step-Down Regulator                      |                          |                                                                         |       |      |       |          |

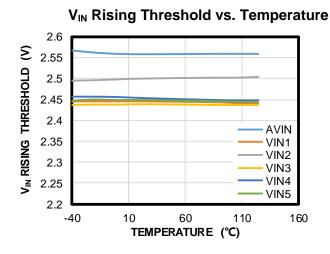

| AVIN UVLO rising                         | V <sub>AIN1_R</sub>      |                                                                         | 2.4   | 2.55 | 2.7   | V        |

| AVIN UVLO hysteresis                     | VAIN1_HYS                |                                                                         |       | 300  |       | mV       |

| VIN1 UVLO rising                         | V <sub>IN1_R</sub>       |                                                                         | 2.3   | 2.45 | 2.6   | V        |

| VIN1 UVLO hysteresis                     | V <sub>IN1_HYS</sub>     |                                                                         |       | 300  |       | mV       |

| VIN2 UVLO rising                         | V <sub>IN2_R</sub>       |                                                                         | 2.35  | 2.5  | 2.65  | V        |

| VIN2 UVLO hysteresis                     | V <sub>IN2_HYS</sub>     |                                                                         |       | 300  |       | mV       |

| VIN3 UVLO rising                         | V <sub>IN3_R</sub>       |                                                                         | 2.3   | 2.45 | 2.6   | V        |

| VIN3 UVLO hysteresis                     | V <sub>IN3_HYS</sub>     |                                                                         |       | 300  |       | mV       |

| VIN4 UVLO rising                         | V <sub>IN4_R</sub>       |                                                                         | 2.3   | 2.45 | 2.6   | V        |

| VIN4 UVLO hysteresis                     | V <sub>IN4_HYS</sub>     |                                                                         |       | 300  |       | mV       |

| VIN5 UVLO rising                         | V <sub>IN5_R</sub>       |                                                                         | 2.3   | 2.45 | 2.6   | V        |

| VIN5 UVLO hysteresis                     | V <sub>IN5_HYS</sub>     |                                                                         |       | 300  |       | mV       |

|                                          | $V_{FB1}$                | Default output of buck 1                                                | 1.127 | 1.15 | 1.173 | V        |

|                                          | $V_{FB2}$                | Default output of buck 2                                                | 1.47  | 1.5  | 1.53  | V        |

| Feedback voltage accuracy                | $V_{FB3}$                | Default output of buck 3                                                | 1.127 | 1.15 | 1.173 | V        |

|                                          | V <sub>FB4</sub>         | Default output of buck 4                                                | 1.764 | 1.8  | 1.836 | V        |

| Maximum duty cycle (11)                  | D <sub>MAX</sub>         | Buck 1 to buck 4                                                        |       | 100  |       | %        |

| Buck 1, Buck 3 (4.5A/4.5A)               |                          |                                                                         |       |      |       | <u> </u> |

| , - (                                    | HS <sub>RDS-ON1</sub>    |                                                                         |       | _    | _     | _        |

|                                          | HS <sub>RDS-ON3</sub>    | 500mA, T <sub>J</sub> = 25°C                                            |       | 25   | 35    | mΩ       |

| HS-FET on resistance                     | HS <sub>RDS-ON1</sub>    | 500mA, T <sub>J</sub> = -40°C to +125°C                                 |       | 25   | 45    | mΩ       |

|                                          | HS <sub>RDS-ON3</sub>    | SouthA, IJ = -40°C to +125°C                                            |       | 20   | 70    | 11122    |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN1} = V_{IN2} = V_{IN3} = V_{IN4} = V_{IN5} = AVIN = 5V, T_J = -40^{\circ}C \ to \ +125^{\circ}C^{(9)}, typical \ value \ is tested \ at \ T_J = 25^{\circ}C, unless \ otherwise \ noted.$

| Parameter                     | Symbol                | Condition                                              | Min                            | Тур                                              | Max  | Units              |

|-------------------------------|-----------------------|--------------------------------------------------------|--------------------------------|--------------------------------------------------|------|--------------------|

|                               | LS <sub>RDS-ON1</sub> | 500 T. A. T                                            |                                | 40                                               | 40   | 0                  |

| LO EET on modiation of        | LS <sub>RDS-ON3</sub> | 500mA, T <sub>J</sub> = 25°C                           |                                | 12                                               | 16   | mΩ                 |

| LS-FET on resistance          | LS <sub>RDS-ON1</sub> | 500 TA T 4000 AT 140500                                |                                | 40                                               | 00   | 0                  |

|                               | LS <sub>RDS-ON3</sub> | $500$ mA, $T_J = -40$ °C to $+125$ °C                  |                                | 12                                               | 20   | mΩ                 |

| Cuitab lankaga 4              | HSW <sub>ILK1</sub>   | EN = 0V, V <sub>IN</sub> = 5.5V,                       |                                | 0                                                | 4    |                    |

| Switch leakage 1              | HSW <sub>ILK3</sub>   | SW = 0V or 5.5V, $T_J = 25$ °C                         |                                | U                                                | 1    | μA                 |

| Switch lookage 2              | LSW <sub>ILK1</sub>   | $EN = 0V, V_{IN} = 5.5V,$                              |                                | 0                                                | 1    |                    |

| Switch leakage 2              | LSW <sub>ILK3</sub>   | SW = 0V or 5.5V, $T_J = 25$ °C                         |                                | U                                                | 1    | μA                 |

| High-side current limit       | ILIMIT1               | $T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$   | 7.4                            | 9.3                                              | 11.4 | Α                  |

| riigii-side current iiriit    | I <sub>LIMIT3</sub>   | $T_{J} = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | 7.4                            | 9.3                                              | 11.4 | Α                  |

| Minimum on time (11)          | ton_min1              |                                                        | 12 to +125°C  12 to +125°C  7, |                                                  | ns   |                    |

| William on time V             | t <sub>ON_MIN3</sub>  |                                                        |                                | 50                                               |      | ns                 |

| Minimum off time (11)         | toff_min1             |                                                        |                                | 120                                              |      | ns                 |

| Willimian on time (17)        | toff_min3             |                                                        |                                | 120                                              |      | ns                 |

| Output discharge resistance   | R <sub>O_DIS1</sub>   |                                                        | 3                              | 7                                                | 20   | Ω                  |

| Coff start times              | t <sub>SS_B1</sub>    | V <sub>OUT</sub> = 10% to 90%                          | 140                            | 300                                              | 430  | μs                 |

| Soft-start time               | t <sub>SS_B3</sub>    | t <sub>SS B3</sub> V <sub>OUT</sub> = 10% to 90%       |                                | 300                                              | 430  | μs                 |

| Output OVP rising threshold   | V <sub>OVP1_H</sub>   |                                                        | 115                            | 120                                              | 125  | % V <sub>REF</sub> |

| Output OVP recovery threshold | V <sub>OVP1_L</sub>   |                                                        | 105                            | 110                                              | 115  | % V <sub>REF</sub> |

| Buck 2, Buck 4 (2.5A/2A)      |                       | 1                                                      |                                | ı                                                | I.   | ı                  |

|                               | HS <sub>RDS-ON2</sub> |                                                        |                                | 4.0                                              |      |                    |

| 110 FFT                       | HS <sub>RDS-ON4</sub> | 500mA, T <sub>J</sub> = 25°C                           |                                | 40                                               | 55   | mΩ                 |

| HS-FET on resistance          | HS <sub>RDS-ON2</sub> | SRDS-ON2                                               |                                | 40                                               | 70   |                    |

|                               | HS <sub>RDS-ON4</sub> | $500$ mA, $T_J = -40$ °C to $+125$ °C                  |                                | 40                                               | 70   | mΩ                 |

|                               | LS <sub>RDS-ON2</sub> | 500 A T 25°C                                           |                                | 40                                               |      | O                  |

| LO FET an accietance          | LS <sub>RDS-ON4</sub> | 500mA, T <sub>J</sub> = 25°C                           |                                | 40                                               | 55   | mΩ                 |

| LS-FET on resistance          | LS <sub>RDS-ON2</sub> | 500 TA T 4000 to 140500                                |                                | 40                                               | 0.5  | 0                  |

|                               | LS <sub>RDS-ON4</sub> | $500$ mA, $T_J = -40$ °C to $+125$ °C                  |                                | 40                                               | 85   | mΩ                 |

| Control la alcana O           | HSW <sub>ILK2</sub>   | Shutdown, V <sub>IN</sub> = 5.5V,                      |                                | 0                                                | 4    |                    |

| Switch leakage 3              | HSW <sub>ILK4</sub>   | SW = 0V or 5.5V, $T_A = 25^{\circ}C$                   |                                | 0                                                | 1    | μA                 |

| Switch leakage 4              | LSW <sub>ILK2</sub>   | Shutdown, V <sub>IN</sub> = 5.5V,                      |                                | 0                                                | 4    |                    |

| Switch leakage 4              | LSW <sub>ILK4</sub>   | SW = 0V or 5.5V, $T_A = 25^{\circ}C$                   |                                |                                                  | 1    | μA                 |

| High aids ourrent limit       | I <sub>LIMIT2</sub>   |                                                        | 4.6                            | 6.1                                              | 7.5  | _                  |

| High-side current limit       | ILIMIT4               |                                                        | 4.6                            | 6.1                                              | 7.5  | A                  |

| Minimum on time (11)          | ton_min2              |                                                        |                                | 50                                               |      | ns                 |

|                               | t <sub>ON_MIN4</sub>  |                                                        |                                | 50                                               |      | ns                 |

| Minimum off time (11)         | toff_MIN2             |                                                        |                                | 40 85 r  0 1  0 1  6.1 7.5  6.1 7.5  50  50  100 | ns   |                    |

| Minimum off time (11)         | toff_MIN4             |                                                        |                                | 100                                              |      | ns                 |

| Output discharge resistance   | R <sub>O_DIS2</sub>   |                                                        | 3                              | 7.5                                              | 20   | Ω                  |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN1} = V_{IN2} = V_{IN3} = V_{IN4} = V_{IN5} = AVIN = 5V, T_J = -40^{\circ}C \ to \ +125^{\circ}C^{(9)}, typical \ value \ is tested \ at \ T_J = 25^{\circ}C, unless \ otherwise \ noted.$

| Parameter                     | Symbol               | Condition                                                                             | Min   | Тур  | Max   | Units              |

|-------------------------------|----------------------|---------------------------------------------------------------------------------------|-------|------|-------|--------------------|

| Ooth stantings                | t <sub>SS_B2</sub>   | V <sub>OUT</sub> = 10 to 90%                                                          | 140   | 300  | 430   | μs                 |

| Soft-start time               | t <sub>SS_B4</sub>   | V <sub>OUT</sub> = 10 to 90%                                                          | 140   | 300  | 430   | μs                 |

| Output OVP rising threshold   | $V_{OVP2\_H}$        |                                                                                       | 115   | 120  | 125   | % V <sub>REF</sub> |

| Output OVP recovery threshold | V <sub>OVP2_L</sub>  |                                                                                       | 105   | 110  | 115   | % V <sub>REF</sub> |

| 10mA RTC LDO                  |                      |                                                                                       |       |      |       |                    |

| Default output voltage        | V <sub>RTC_LDO</sub> | I <sub>OUT</sub> = 10mA, power-on state                                               | 3.24  | 3.37 | 3.5   | V                  |

| Ground current                | I <sub>Q_RTC</sub>   | No load                                                                               |       | 6.5  |       | μΑ                 |

| Dropout voltage               | V <sub>DROP1</sub>   | Vout = 3V, Iout = 5mA 50                                                              |       |      | mV    |                    |

| Current limit                 | I <sub>LIM_RTC</sub> | $V_{IN} = 3.3V$ , $V_{OUT}$ drops 33%, $T_J = 25$ °C                                  | 25    | 55   | 85    | mA                 |

| Soft-start slew rate          | t <sub>SS_RTC</sub>  | V <sub>OUT</sub> = 10% to 90%, C <sub>OUT</sub> = 1μF                                 |       | 25   |       | mV/μs              |

| Low-Dropout LDO Regulator     | : LDO2 to L          | DO5                                                                                   |       |      |       |                    |

|                               | $V_{LDO2}$           | I <sub>OUT</sub> = 10mA                                                               | 1.764 | 1.8  | 1.836 | V                  |

| Output valtage                | V <sub>LDO3</sub>    | I <sub>OUT</sub> = 10mA                                                               | 1.764 | 1.8  | 1.836 | V                  |

| Output voltage                | V <sub>LDO4</sub>    | I <sub>OUT</sub> = 10mA                                                               |       | 1.1  | 1.122 | V                  |

|                               | V <sub>LDO5</sub>    | I <sub>OUT</sub> = 10mA                                                               | 1.764 | 1.8  | 1.836 | V                  |

| PSRR (10)                     | PSRR <sub>1K</sub>   | For LDO4 and LDO5, V <sub>OUT</sub> = 1.8V                                            |       | 52   |       | dB                 |

| Dropout voltage               | V <sub>DROP1</sub>   | Vout = 3V, Iout = 300mA                                                               |       | 50   |       | mV                 |

|                               | ILIMIT_LDO           | For LDO2 and LDO3, $V_{IN} = 3.3V$ , $V_{OUT}$ drops 33%                              | 300   | 430  | 600   | mA                 |

| Current limit                 | ILIMIT_LDO_L         | LDO4 and LDO5 set ILIM bit = 0, V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> drops 33%    | 380   | 520  | 660   | mA                 |

|                               | ILIMIT_LDO_H         | LDO4 and LDO5 set ILIM bit = 1,<br>V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> drops 33% | 580   | 790  | 1000  | mA                 |

| Output discharge resistance   | Ro_dis2              |                                                                                       | 3     | 7    | 20    | Ω                  |

| Soft-start time               | t <sub>SS_B2</sub>   | $V_{OUT} = 10\%$ to 90%, $C_{OUT} = 2.2\mu F$                                         |       | 50   |       | μs                 |

| Line regulation               |                      | VIN2 = VIN5 = 2.7V to 5.5V                                                            |       | 0.3  |       | %/V                |

| Load regulation               |                      | VIN2 = VIN5 = 3.3V, I <sub>OUT</sub> from 10mA to 100mA                               |       | 0.5  |       | %                  |

| Logic Pins                    | •                    |                                                                                       |       |      | •     | •                  |

| PWRON pull-up current         | I <sub>PWRON</sub>   | Internal pull-up to AVIN                                                              | 5     | 9    | 13    | μΑ                 |

| PWRON rising threshold        | $V_{PWR\_R}$         |                                                                                       | 0.8   | 1    | 1.2   | V                  |

| PWRON voltage hysteresis      | V <sub>PWR_HYS</sub> |                                                                                       |       | 100  |       | mV                 |

| EN1 rising threshold          | V <sub>EN1_R</sub>   |                                                                                       | 0.8   | 1    | 1.2   | V                  |

| EN1 rising hysteresis         | V <sub>EN1_HYS</sub> |                                                                                       |       | 100  |       | mV                 |

| PG rising threshold           | V <sub>PG_R</sub>    | RSTO_MODE = 01                                                                        | 86%   | 90%  | 94%   | $V_{FB}$           |

| PG falling threshold          | V <sub>PG_F</sub>    | RSTO_MODE = 01                                                                        | 76%   | 80%  | 84%   | V <sub>FB</sub>    |

| PFI rising threshold          | V <sub>PFI_R</sub>   | RSTO_PFI_THLD = 01,<br>adjustable via the I <sup>2</sup> C/MTP                        | 2.78  | 2.9  | 3.02  | V                  |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN1}$  =  $V_{IN2}$  =  $V_{IN3}$  =  $V_{IN4}$  =  $V_{IN5}$  = AVIN = 5V,  $T_J$  = -40°C to +125°C <sup>(9)</sup>, typical value is tested at  $T_J$  = 25°C, unless otherwise noted. <sup>(10)</sup>

| Parameter                                      | Symbol                   | Condition                               | Min | Тур | Max | Units              |

|------------------------------------------------|--------------------------|-----------------------------------------|-----|-----|-----|--------------------|

| PFI hysteresis                                 | V <sub>PFI_HYS</sub>     |                                         |     | 7%  |     | V <sub>PFI_R</sub> |

| RSTO rising delay                              | <b>t</b> <sub>RSTO</sub> | Adjustable via the I <sup>2</sup> C/MTP | 20  | 50  | 70  | ms                 |

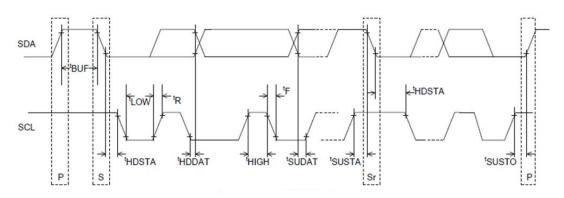

| I <sup>2</sup> C Interface Specifications (12) |                          |                                         | •   |     |     |                    |

| Input logic high                               | V <sub>IH</sub>          |                                         | 1.4 |     |     | V                  |

| Input logic low                                | $V_{IL}$                 |                                         |     |     | 0.4 | V                  |

| Output voltage logic low                       | $V_{OUT\_L}$             | RSTO pin sink 4mA                       |     |     | 0.4 | V                  |

| SCL clock frequency                            | fscL                     |                                         |     |     | 3.4 | MHz                |

| SCL high time                                  | tніgн                    |                                         | 60  |     |     | ns                 |

| SCL low time                                   | $t_{LOW}$                |                                         | 160 |     |     | ns                 |

| Data set-up time                               | tsu_dat                  |                                         | 10  |     |     | ns                 |

| Data hold time                                 | thd_dat                  |                                         |     | 70  |     | ns                 |

| Set-up time for repeated start                 | <b>t</b> su_sta          |                                         | 160 |     |     | ns                 |

| Hold time for repeated start                   | t <sub>HD_STA</sub>      |                                         | 160 |     |     | ns                 |

| Bus free time between start and stop condition | <b>t</b> BUF             |                                         | 160 |     |     | ns                 |

| Set-up time for stop condition                 | <b>t</b> su_sto          |                                         | 160 |     |     | ns                 |

| SCL and SDA rise time                          | t <sub>R</sub>           |                                         | 10  |     | 300 | ns                 |

| SCL and SDA fall time                          | t <sub>F</sub>           |                                         | 10  |     | 300 | ns                 |

| Pulse width of suppressed spike                | <b>t</b> sp              |                                         | 0   |     | 50  | ns                 |

| Capacitance bus for each bus line              | Св                       |                                         |     |     | 400 | pF                 |

#### Notes:

- 9) Not tested in production, guaranteed by over-temperature correlation.

- 10) Tested with default version MP5479GRM-0003.

- 11) Guaranteed by engineering sample characterization.

- 12) It is recommended to begin operating the I<sup>2</sup>C function after the power-on sequence is complete (all enabled power rails have finished starting up). See the I<sup>2</sup>C timing chart below when reading I<sup>2</sup>C interface specifications.

I<sup>2</sup>C Timing Diagram

Efficiency

### TYPICAL CHARACTERISTICS

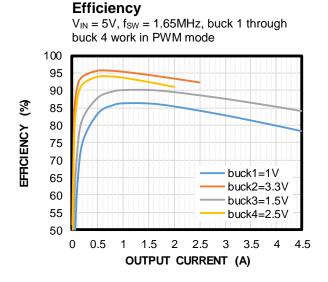

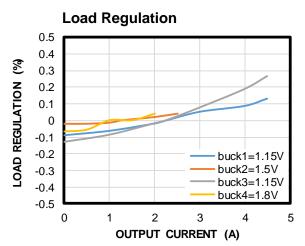

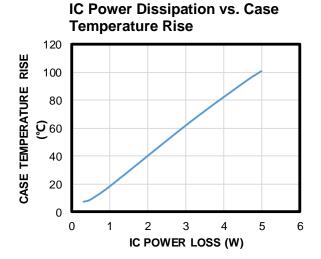

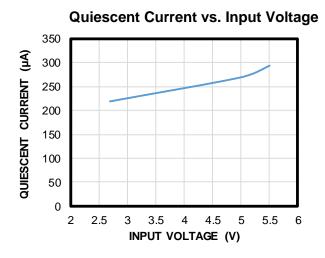

Performance waveforms are tested on the evaluation board,  $V_{IN} = 5V$ ,  $T_A = 25$ °C, tested using MP5479-0003 parts, unless otherwise noted.

#### $V_{IN} = 5V$ , $f_{SW} = 2.2MHz$ , buck 1 through buck 4 work in PWM mode 100 95 90 8 85 80 **EFFICIENCY** 75 70 buck1=1.15V 65 buck2=1.5V 60 buck3=1.15V 55 buck4=1.8V 50 3.5 0.5 1 1.5 2 2.5 3 **OUTPUT CURRENT (A)**

## TYPICAL CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board,  $V_{IN}$  = 5V,  $T_A$  = 25°C, tested using MP5479-0003 parts, unless otherwise noted.

# Switching Frequency vs. Temperature

### TYPICAL PERFORMANCE CHARACTERISTICS

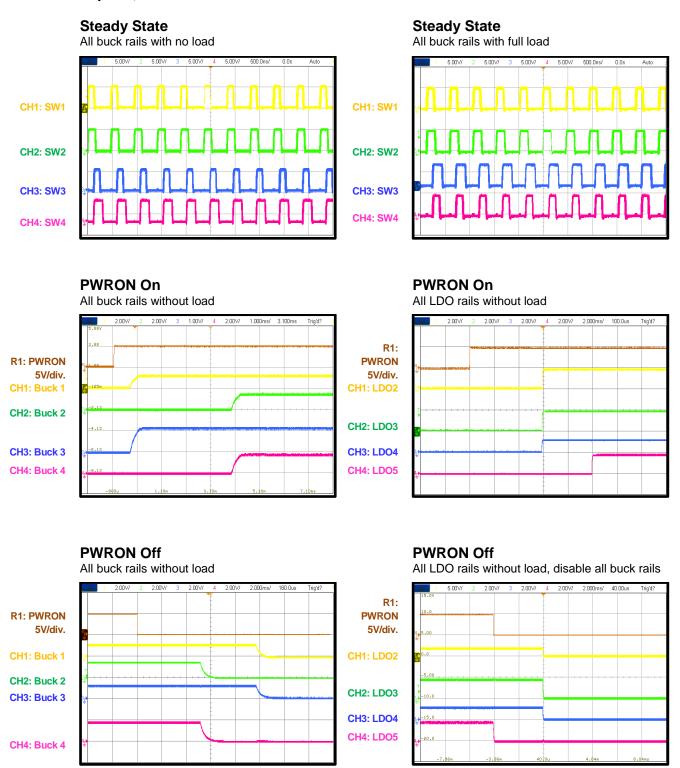

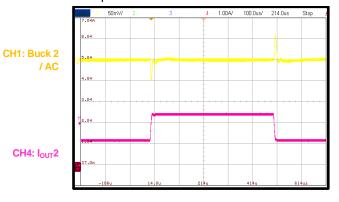

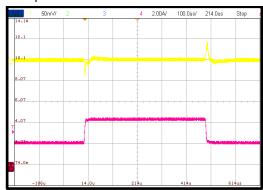

Performance waveforms are tested on the evaluation board,  $V_{IN}$  = 5V,  $T_A$  = 25°C, tested using MP5479-0003 parts, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board,  $V_{IN}$  = 5V,  $T_A$  = 25°C, tested using MP5479-0003 parts, unless otherwise noted.

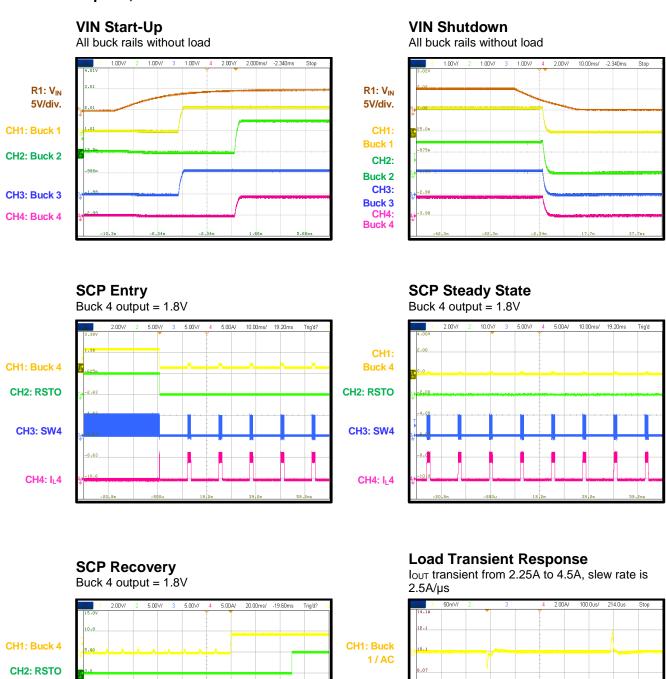

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board,  $V_{IN}$  = 5V,  $T_A$  = 25°C, tested using MP5479-0003 parts, unless otherwise noted.

CH1: Buck

CH4: I<sub>OUT</sub>3

3/AC

#### **Load Transient Response**

$I_{OUT}$  transient from 1.25A to 2.5A, slew rate is 2.5A/µs

#### **Load Transient Response**

$l_{\text{OUT}}$  transient from 2.25A to 4.5A, slew rate is 2.5A/µs

### **Load Transient Response**

$I_{OUT}$  transient from 1A to 2A, slew rate is 2.5A/µs

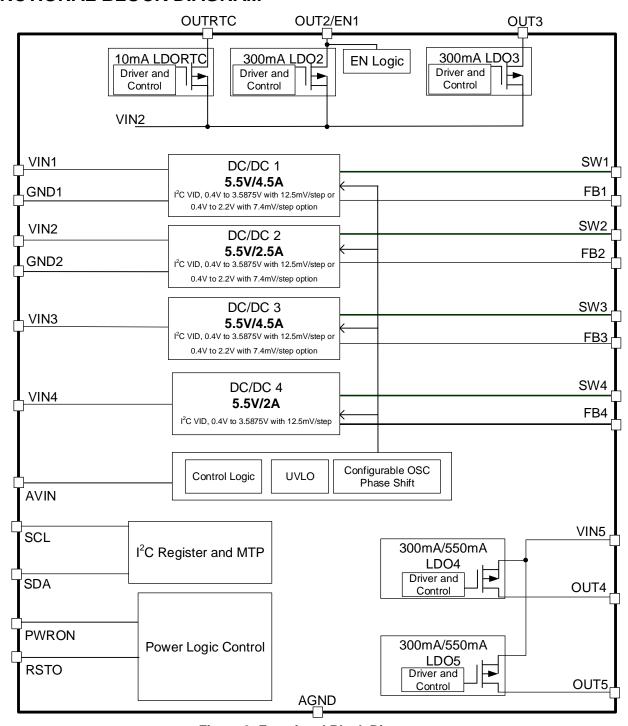

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

#### **OPERATION**

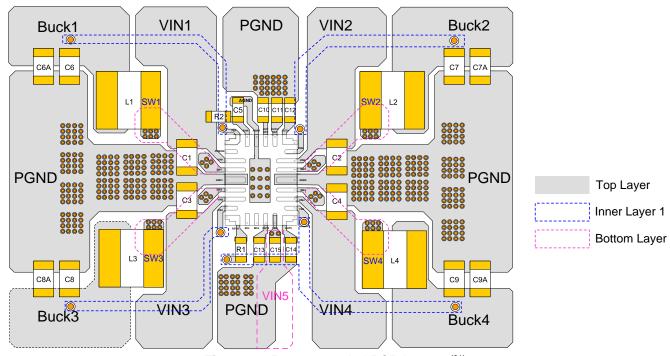

The MP5479 provides a complete power management solution for 5V systems, including infotainment, video recorders, and more. It 4-channel integrates four high-frequency, synchronous rectified, step-down, switch-mode converters and five low-dropout regulators. With all components inside a compact QFN-26 (3.5mmx4.5mm) package, it greatly reduces component count and PCB space.

The I<sup>2</sup>C and MTP interfaces provide an adjustable default output voltage, power-on sequence, and dynamic voltage scaling. In addition, the I2C provides powerful logic functions. See the Register Map section on page 26 for more details.

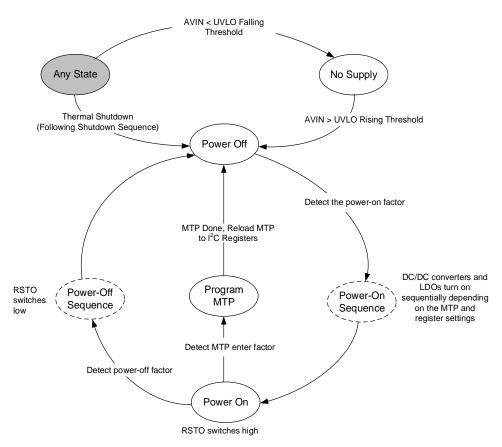

Figure 3: Power Control State Machine Diagram

# **Power Control**

#### **State Machine Description**

The state machine (see Figure 3) has a number of status options, including no supply, power off, power-on sequence, power on, power-off sequence, program MTP, and shutdown. These statuses are described below.

#### No Supply

The PMIC's input pin has a UVLO detection circuit. If the input voltage (AVIN) is below the

UVLO rising threshold, all of the PMIC's functions are disabled.

#### Power Off

All power rails are powered off. When AVIN exceeds its rising UVLO, the PMIC enters the power-off state. In this state, the PMIC is always monitoring the power-on factors; once a poweron factor is detected, the device changes to the power-on sequence state.

#### Power-On Sequence

The DC/DC converters and LDOs turn on sequentially according to the order programmed by the MTP e-fuse.

#### Power On

The DC/DC converters and LDOs are turned on. The RSTO pin's output switches high. In this state, the PMIC is always monitoring the poweroff and program MTP factors.

#### **Power-Off Sequence**

The PMIC enters this sequence when it detects the power-off factors during a power on state. First, the RSTO is switched low, then the DC/DC converters and LDOs turn off sequentially according to the order programmed by the MTP e-fuse.

### **Program MTP**

The PMIC shuts down all buck regulators and LDOs with the power-off sequence when entering program MTP mode. After MTP programming is complete, the PMIC reloads the MTP to the I<sup>2</sup>C registers and then monitors for power-on factors.

#### Shutdown Event

If the PMIC detects any of the conditions shown below, it immediately changes to a no supply or power off state, regardless of the current state.

- If the input voltage is below the UVLO falling threshold, the device enters a no supply state.

- If over-temperature protection (OTP) is triggered, the device enters a power-off state.

#### Note:

13) If the PMIC enters a power-off state due to OTP being triggered, then LDORTC is off.

#### **Power-On Factor**

The PMIC has several power-on factors, including PWR ON, thermal recovery, and EN1. These factors are described below.

#### **PWRON ON**

If the PWRON pin is pulled to logic high (PWRON MODE = 0) or there is a falling edge on the PWRON pin (PWRON MODE = 1), the PMIC enters the power-on sequence. See the PWRON Functions section on page 21 for more details.

#### Thermal Recovery

The part enters a power off state if the die temperature exceeds the thermal protection threshold. Once the die temperature falls below the threshold, the PMIC enters the power-on sequence again.

#### EN1

If pin 23 is selected as EN1, and EN1 is pulled to logic high (EN1 INV defines EN1's active high) or EN1 is pulled to logic low (EN1 INV defines EN1's active low), then the power rails controlled by EN1 enter the power-on sequence. See the EN1 Functions section on page 23 for more details.

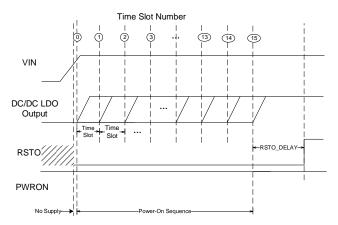

#### **Power-On Sequence**

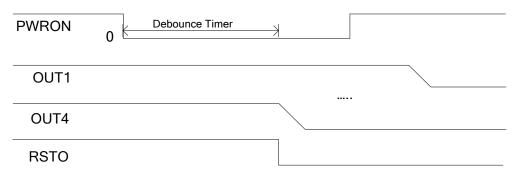

There are 16 time slots for the power-on sequence. All of the DC/DC converters and LDOs except OUTRTC LDO can programmed between 0 and 15 time slots by the MTP e-fuse. The delay time between each time slot is adjustable with the MTP TIME\_SLOT bits. The time does not change with the switching frequency.

RSTO switches high with the RSTO DELAY time when the power-on sequence is complete. The DC/DC converter and LDO power-on sequence are set by POWER\_ON\_SLOT\_NO PWR\_ON\_TIME\_SLOT\_MODE, respectively. See the MTP table on page 28 for details.

Figure 4: Power-On Sequence

#### **OUTRTC ON**

The OUTRTC LDO is always on if both VIN2 and AVIN are above their respective UVLO rising thresholds, regardless of any other pin statuses. OUTRTC turns off if either VIN2 or AVIN fall below their respective UVLO falling thresholds or if thermal shutdown is triggered.

#### Other Buck Regulators and LDOs On

The MP5479 provides a programmable powersequence. See the MTP E-Fuse on Configuration Table on page 26 for details on bits to set the time slot number for each channel.

#### **Power-Off Factor**

The PMIC power-off factors are PWRON OFF and EN1. They are described below.

#### **PWRON OFF**

If the PWRON pin is pulled to logic low (PWRON MODE = 0) or a falling edge on the PWRON pin (PWRON\_MODE = 1), the PMIC enters a power-off sequence. See the PWRON Functions section on page 21 for more details.

#### EN1

If pin 23 is selected as EN1, and EN1 is pulled to logic low (EN1 INV defines EN1 as active high) or EN1 is pulled to logic high (EN1 INV defines EN1 as active low), then the power rails controlled by EN1 enter the power-off sequence. See the EN1 Functions section on page 23 for more details.

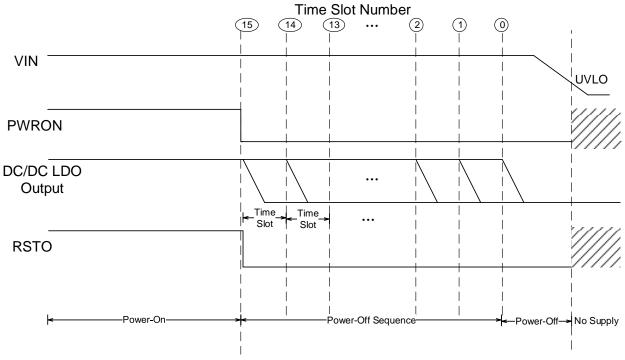

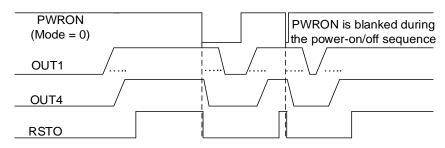

#### **Power-Off Sequence**

There are 16 time slots for the power-off sequence. All of the DC/DC converters and except OUTRTC LDO, can programmed between 0 and 15 time slots by the MTP e-fuse. The delay time between each time slot is adjustable with the MTP TIME\_SLOT bits. The time does not change with the switching frequency.

The power-off sequence begins at the maximum used time slot number. Therefore, the power-off sequence does not always start from time slot 15.

RSTO is pulled low prior to the DC/DC converters and LDOs starting to turn off. The DC/DC converter and LDO power-off sequence are set by POWER\_OFF\_SLOT\_NO and POWER\_OFF\_SLOT\_MODE. See the MTP E-Fuse Configuration Table on page 26 for more details.

Figure 5: Power-Off Sequence (PWRON\_MODE = 0)

### **Program MTP**

en1interface must strictly follow the steps below:

- 1. Ensure that all bucks and LDOs have no load before programming the MTP e-fuse.

- 2. Write the correct MTP program password to register 0x26.

- 3. Set ENTER\_MTP\_MODE = 1 to enter MTP program mode. All buck regulators and LDOs shut down in this mode.

- 4. Write the desired content to the I<sup>2</sup>C registers.

- 5. Increase the VIN1 and AVIN power supply to between 6.4V and 6.5V with a minimum 150mA current capability.

- 6. Set PROGRAM\_MTP = 1 to start the MTP efuse program.

- The PMIC calculates the sum of all related I<sup>2</sup>C registers to be burned to the MTP register. The checksum result is also written to the MTP register.

- 8. After the MTP write operation finishes (typically takes 100ms), the PMIC sets the PROGRAM\_MTP bit to 0, and the I<sup>2</sup>C register write protection is unlocked. ENTER MTP MODE is also set to 0.

- After MTP programming, the MP5479 reloads the MTP to the related I<sup>2</sup>C registers and the PWRON pin function is re-enabled. The buck and LDO regulators then power up based on their power-on factors. After the power-on sequence completes, I<sup>2</sup>C communication is enabled.

- Decrease the VIN1 and AVIN voltage to <5.5V, then restart the power supply for normal operation.

During VIN power-up, before loading the MTP data into the I<sup>2</sup>C register, the PMIC does a checksum calculation for all related MTP registers, then compares it with the checksum byte. If they match, the MTP data is loaded into the I<sup>2</sup>C register. If not, the I<sup>2</sup>C register uses the hard-coded default value. There is an I<sup>2</sup>C register flag bit to indicate a checksum error.

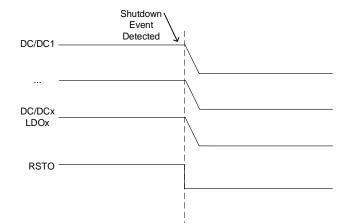

#### **Shutdown Sequence**

If the input voltage is below the UVLO falling threshold or if the IC is over-temperature, the PMIC enters the shutdown sequence

immediately. All of the DC/DC and LDO regulators turn off at the same time.

Figure 6: Shutdown Sequence

#### **High-Efficiency Buck Regulator**

Buck 1 through buck 4 are synchronous, step-down DC/DC converters that have built-in UVLO, soft start, compensation, and hiccup current limit protection. Fixed-frequency, constant-on-time (COT) control provides fast transient response. The switching clock is phase-shifted from buck 1 through buck 4 during CCM operation. Buck 1 through buck 4 support 100% duty cycle mode.

### **Power Supply and UVLO**

VIN1 is the power supply for buck 1. VIN2 is the power supply for buck 2, LDORTC, LDO2, and LDO3. VIN3 is the power supply for buck 3. VIN4 is the supply for buck 4. VIN5 is the power supply for LDO4 and LDO5. AVIN is the power input to bias the internal logic blocks.

VIN1, VIN2, VIN3, VIN4, VIN5, and AVIN have their own UVLO thresholds with proper hysteresis. Once AVIN ramps up and exceeds the UVLO rising threshold, the PWRON logic is enabled and ready to accept start-up and shutdown commands. LDORTC is active once VIN2 exceeds its rising threshold.

#### **Internal Soft Start**

Soft start is implemented to prevent the PMIC output voltage from overshooting during start-up. When the PMIC starts up, the internal circuitry of each power rail generates a soft-start voltage that ramps up from 0V. The soft-start period lasts until the voltage on the soft-start capacitor exceeds the reference voltage. At this point, the reference voltage takes over.

For the four 4-channel buck outputs, the soft-start times are MTP-adjustable. For the LDO2 through LDO5 outputs, the soft-start times are internally fixed at 50µs. For LDORTC, the soft-start slew rate is consistent at 25mV/µs.

#### **Output Discharge**

In order to discharge the output capacitor during the power-off sequence, there is a passive discharge path from the DC/DC converters' and LDOs' output to ground. The discharge path is turned on when its corresponding channel is disabled. The typical discharge resistance is  $7\Omega$ . The discharge function can be enabled or disabled through the  $I^2C$  interface.

#### **Over-Voltage Protection (OVP)**

The MP5479 monitors the feedback voltage to detect possible over-voltage conditions. When the feedback voltage exceeds 120% of the target voltage, the controller turns off both the high-side MOSFET (HS-FET) and low-side MOSFET (LS-FET), and the discharge path is turned on. The part exits this regulation period once the feedback voltage falls below 110% of the reference voltage.

#### **Over-Current Protection (OCP)**

If the peak inductor current reaches its limit (set via the I<sup>2</sup>C registers) when the HS-FET is on, OCP is triggered. The LS-FET is forced on until the inductor current drops to the valley current

limit; then the HS-FET turns on again. The part does not exit OCP unless the inductor peak current falls below the limit. If the OCP time lasts for longer than 150µs (typical), the buck enters hiccup mode.

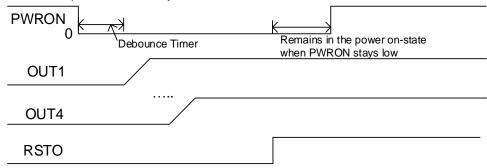

### System Control Signals PWRON Functions

PWRON is an input pin to the IC that generates a power-on or power-off event. This pin can be configured to detect a level or a falling edge via the MTP.

When the PWRON\_MODE bit = 1, the PWRON\_DEBOUNCE\_TIMER bit can set the PWRON pin's debounce timer to filter out mechanical switch short press noise.

When the PWRON\_MODE bit = 0, PWRON works as an enable pin. Apply a logic high voltage to turn the PMIC on; apply a logic low voltage to turn the PMIC off.

# PWRON\_MODE = 1 (Edge Trigger) Power On

If AVIN is above the UVLO threshold and PWRON is asserted low for longer than PWRON\_DEBOUNCE\_TIMER when the PMIC is powered off, the power-on sequence begins. The power-on sequence must complete, and then the PWRON detection function is reenabled.

Figure 7: PWRON\_MODE = 1, Press PWRON to Power On

#### **Power Off**

If PWRON asserts low for longer than PWRON\_DEBOUNCE\_TIMER when the device is powered on, the power-off sequence begins. The MP5479 turns off all regulators and LDOs (except OUTRTC). The power-off sequence is pre-configured by the MTP e-fuse.

If the PWRON pin is still pulled low after the power-off sequence completes, the MP5479 remains in its power off state. If the PWRON pin is pulled high after the power-off sequence completes, the MP5479 continues the power-off sequence.

Figure 8: PWRON\_MODE = 1, Press PWRON to Power Off

## PWRON\_MODE = 0 (Level Trigger)

The PMIC enters the power-on sequence once the input voltage (AVIN) exceeds its UVLO threshold and PWRON is pulled high.

If PWRON is pulled low when the MP5479 is powered on, the device executes the power-off sequence. If PWRON is pulled high when the MP5479 is powered off, the MP5479 executes a

power-on sequence. During a power-on or power-off sequence, the PWRON pin function is blanked until the sequence is complete. For example, during a power-off sequence, even if PWRON is pulled high, the PMIC finishes the power-off sequence first, then executes the power-on sequence (see Figure 9).

Figure 9: PWRON Enable and Disable Function

Figure 10: EN1 Function

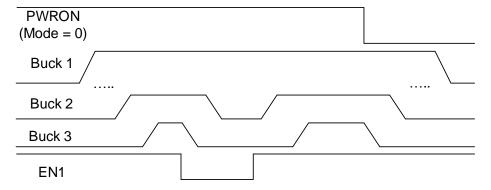

#### **EN1 Functions**

EN1 is a multi-function pin with an LDO2 output. If the EN1 function is selected on pin 23, the MP5479 supports the operations described below.

The EN1 pin can be used to control the power rails' on/off sequence. This is very useful for non-I<sup>2</sup>C interface applications.

Figure 10 shows EN1 function. For example, EN1 controls buck 2 and buck 3, and EN1\_INV is selected as active high. When EN1 is pulled low, buck 2 and buck 3 power off sequentially. When EN1 is pulled high, buck 2 and buck 3 power on sequentially. EN1\_INV defines EN1 as active high or active low. PWRON has higher priority than EN1, so when PWRON is pulled low, all power rails enter the power-off sequence. The buck and LDO regulator enable/disable functions are controlled by both the PWRON and EN1 pins.

#### **Thermal Warning and Shutdown**

Thermal warning and shutdown prevent the part from operating at exceedingly high temperatures.

When the silicon die temperature exceeds 120°C, the MP5479 sets the OTWARNING bit to 1. When the temperature falls to 97°C, this bit can be cleared by writing 1 to it.

If the die temperature exceeds 153°C, the MP5479 sets the OTEMPP bit to 1, and the system enters the shutdown sequence. When the temperature falls to 130°C, the regulator enters the power-on sequence again.

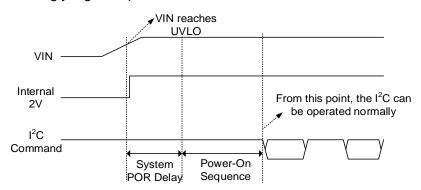

#### I<sup>2</sup>C Timing

The PMIC's I<sup>2</sup>C interface is powered by an internal, fixed, 2V power supply. When VIN exceeds its under-voltage lockout (UVLO) threshold during VIN power-up, this indicates that the 2V LDO power supply is ready. The I<sup>2</sup>C function is disabled during the power-on sequence. When the power-on sequence is complete (for all enabled power rails), the I<sup>2</sup>C is available (see Figure 11).

When the I<sup>2</sup>C is not used, SCL and SDA should be pulled high by a resistor.

Figure 11: I<sup>2</sup>C Timing Graph

#### I<sup>2</sup>C INTERFACE

#### I<sup>2</sup>C Serial Interface Description

The I<sup>2</sup>C is a two-wire, bidirectional serial interface consisting of a data line (SDA) and a clock line (SCL). The lines are externally pulled to a bus voltage when they are idle. A master device is connected to the line; it generates the SCL signal and device address, and arranges the communication sequence.

The MP5479 interface is an I<sup>2</sup>C slave that can support fast mode (400kHz) and high-speed mode (3.4Mhz). The I<sup>2</sup>C interface adds flexibility to the power supply solution. Among other parameters, the output voltage and transition slew rate can be instantaneously controlled by the I<sup>2</sup>C interface. If the master sends the address as an 8-bit value, the 7-bit address should be followed by 0 or 1 to indicate a read or write (R/W) operation, respectively.

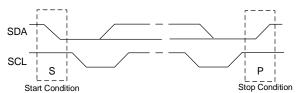

## **Start and Stop Conditions**

The start and stop conditions are signaled by the master device, and signify the beginning and the end of the I<sup>2</sup>C transfer. The start (S) condition is defined as the SDA signal transitioning from high to low while the SCL is high. The stop (P) condition is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 12).

The master then generates the SCL clocks, and transmits the device address and the R/W direction bit on the SDA line.

Figure 12: Start and Stop Conditions

#### **Transfer Data**

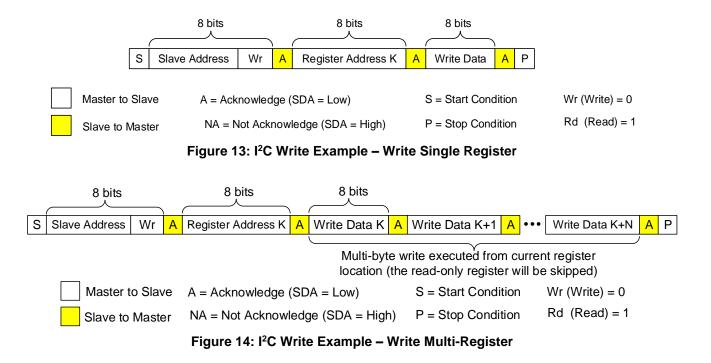

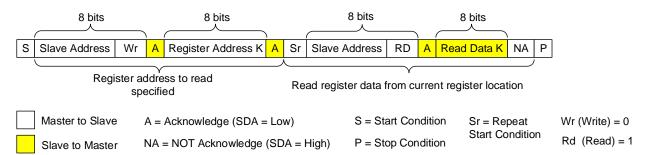

Data is transferred in 8-bit bytes by the SDA line. Each byte of data should be followed by an acknowledge (ACK) bit.

#### I<sup>2</sup>C Update Sequence

The MP5479 requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single data update. After receiving each byte, the MP5479 acknowledges the byte by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the MP5479. The MP5479 performs an update on the falling edge of the LSB byte. Figure 13, Figure 14, and Figure 15 show examples of I<sup>2</sup>C write and read sequences.

Figure 15: I<sup>2</sup>C Read Example – Read Single Register

## **REGISTER DESCRIPTION**

## **MTP E-Fuse Configuration Table**

| OFFSET | NAME       | D7             | D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D5                   | D4            | D3                                      | D2                | D1                | D0                             |

|--------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|-----------------------------------------|-------------------|-------------------|--------------------------------|

| 00     | CTL0       | DVS SLE        | W RATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FREQUE               | NCY           | N/A                                     | PWRON_DEB         | OUNCE_TIMER       | N/A                            |

| 01     | CTL1       | RSTO_I         | MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RSTO_DE              | LAY           | RSTO_PFI_THLD N/A                       |                   |                   |                                |

| 02     | CTL2       | N/A            | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N/A                  |               | TIME_SLOT PWR_ON_<br>TIME_SLOT_<br>MODE |                   |                   | PWR_OFF_<br>TIME_SLOT_<br>MODE |

| 03     |            |                | L.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BUCK1_VRE            | F: 0.4V to 3  | .5875V/12.5mV or                        | 0.4V to 2.2V/7.4i |                   |                                |

| 04     | Buck 1     | N/A            | OVPEN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DISCHGEN<br>1        | MODE<br>BUCK1 |                                         | N                 | /A                |                                |

| 05     | Buck I     | ILI            | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PHASE_D              |               | SOFTS                                   | TART1             | N/                | A                              |

| 06     |            | F              | POWER_OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _SLOT_NO_B1          |               |                                         | POWER_ON_         | SLOT_NO_B1        |                                |

| 07     |            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | F: 0.4V to 3  | .5875V/12.5mV or                        | 0.4V to 2.2V/7.4i | mV                |                                |

| 08     | Buck 2     | N/A            | OVPEN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DISCHGEN<br>2        | MODE<br>BUCK2 |                                         | N.                | /A                |                                |

| 09     | Duon 2     | ILI            | M2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PHASE_D              |               | SOFTS                                   | TART2             | N/                | A                              |

| 0A     |            | F              | POWER_OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _SLOT_NO_B2          |               |                                         | POWER_ON_         | SLOT_NO_B2        |                                |

| 0B     |            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BUCK3_VRE            | F: 0.4V to 3  | .5875V/12.5mV or                        | 0.4V to 2.2V/7.4i | mV                |                                |

| 0C     | Buck 3     | N/A            | OVPEN3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DISCHGEN<br>3        | MODE<br>BUCK3 |                                         | N                 | /A                |                                |

| 0D     | Duck 3     | ILI            | M3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PHASE_D              |               | SOFTS                                   | TART3             |                   |                                |

| 0E     |            | F              | POWER_OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _SLOT_NO_B3          |               |                                         | POWER_ON_         | SLOT_NO_B3        |                                |

| 0F     |            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | В                    | UCK4_VRE      | F: 0.4V to 3.5875V                      | /12.5mV           |                   |                                |

| 10     | Buck 4     | N/A            | OVPEN4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DISCHGEN<br>4        | MODE<br>BUCK4 | N/A                                     |                   |                   |                                |