# 6A, High-Efficiency, Synchronous, Step-Down Switcher with I<sup>2</sup>C Interface

The Future of Analog IC Technology

# NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MP8847

#### DESCRIPTION

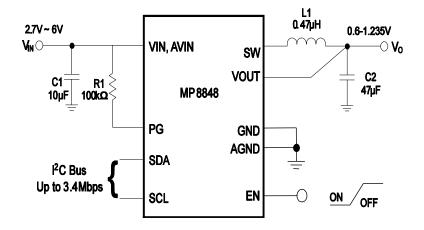

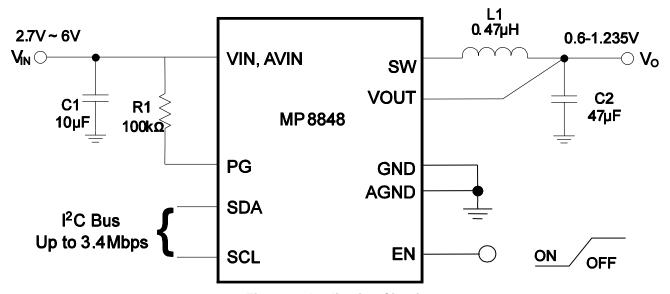

The MP8848 is a highly integrated, high-frequency, synchronous, step-down switcher with an I<sup>2</sup>C control interface. The MP8848 can support up to 6A of load current over an input supply range from 2.7V to 6V with excellent load and line regulation.

Constant-frequency hysteretic mode provides an extremely fast transient response without loop compensation to achieve high efficiency easily under light-load condition.

The output voltage level can be controlled onthe-fly through a 3.4Mbps I<sup>2</sup>C serial interface. The voltage range can be adjusted from 0.6V to 1.235V in 5mV steps. The voltage slew rate, switching frequency, and power-saving mode are also selectable through the I<sup>2</sup>C interface.

Full protection features include internal soft start, over-current protection (OCP), and overtemperature protection (OTP).

The MP8848 requires a minimal number of readily available, standard, external components and is available in a compact QFN-15 (2mmx3mm) package.

#### **FEATURES**

- 2.7V to 6V Input Voltage Range

- Up to 6A Load Current

- Internal  $32m\Omega$  High-Side and  $15m\Omega$  Low-Side Power MOSFETs

- I<sup>2</sup>C-Compatible Interface up to 3.4Mbps

- I<sup>2</sup>C-Programmable Output Range from 0.6V to 1.235V in 5mV Steps

- Factory Adjustable Switching Frequency from 0.85MHz to 2.2MHz

- Power-Saving Mode Selectable via I<sup>2</sup>C

- Internal 1ms Soft Start

- Power Good Indicator

- Current Overload and Thermal Shutdown Protection

- Available in a QFN-15 (2mmx3mm) Package

# **APPLICATIONS**

- Processor Core Supplies

- Micro Converters

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

# TYPICAL APPLICATION

### ORDERING INFORMATION

| Part Number* | Package          | Top Marking |  |

|--------------|------------------|-------------|--|

| MP8848GD     | QFN-15 (2mmx3mm) | See Below   |  |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP8848GD-Z)

### **TOP MARKING**

AVV

YWW

LLL

AVV: Product code of MP8848GD

Y: Year code WW: Week code LLL: Lot number

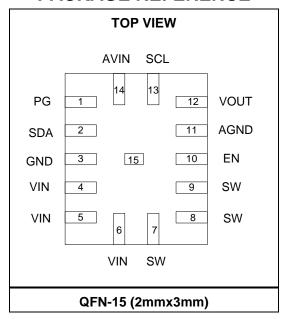

# **PACKAGE REFERENCE**

| ABSOLUTE MAXIMUM RATINGS (1)                                 |

|--------------------------------------------------------------|

| Supply voltage (VIN)0.3V to 7V                               |

| V <sub>SW</sub> 0.3V (-5V for <10ns) to                      |

| 6.5V (8V for <10ns or 10V for <3ns)                          |

| All other pins0.3V to 6.5V                                   |

| Junction temperature 150°C                                   |

| Lead temperature260°C                                        |

| Continuous power dissipation $(T_A = +25^{\circ}C)^{(2)(4)}$ |

| QFN-15 (2mmx3mm)3.5W                                         |

| Storage temperature65°C to 150°C                             |

| Recommended Operating Conditions (3)                         |

| Supply voltage (VIN)2.7V to 6V                               |

| Output voltage (VOUT) 0.6V to 1.235V                         |

| Operating junction temp. (T <sub>J</sub> )40°C to +125°C     |

| Thermal Resistance          | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}$ JC |

|-----------------------------|-------------------------|-----------------------|

| QFN-15 (2mmx3mm)            |                         |                       |

| EV8848-D-00A <sup>(4)</sup> | 35                      | 8 °C/W                |

| JESD51-7 <sup>(5)</sup>     | 70                      | 15 °C/W               |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on EV8848-D-00A, 4-layer PCB.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

VIN = 5V,  $T_J$  = -40°C to +125°C <sup>(6)</sup>, typical value is tested at  $T_J$  = +25°C. The limit over temperature is guaranteed by characterization, unless otherwise noted.

| Parameter                       | Symbol             | Condition                                                                          | Min   | Тур   | Max   | Units |

|---------------------------------|--------------------|------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Input voltage range             | V <sub>IN</sub>    |                                                                                    | 2.7   |       | 6     | V     |

| Quiescent current               | IQ                 | EN = 1.8V, no switching, PFM mode                                                  |       | 300   |       | μΑ    |

| Shutdown current                | Is                 | EN = GND, T <sub>J</sub> = 25°C                                                    |       |       | 1     | μA    |

| Internal reference voltage      | VREF               | $T_J = 25^{\circ}C$                                                                | 0.591 | 0.600 | 0.609 | V     |

| internal reference voltage      | VNEF               | -40°C < T <sub>J</sub> < 125°C                                                     | 0.585 | 0.600 | 0.615 | V     |

| Lowest output voltage           | V <sub>LOW</sub>   | Register = 00h, T <sub>J</sub> = 25°C                                              | 0.591 | 0.600 | 0.609 | V     |

| Lowest output voltage           | <b>V</b> LOW       | -40°C < T <sub>J</sub> < 125°C                                                     | 0.585 | 0.600 | 0.615 | V     |

| Highest output voltage          | V <sub>HIGH</sub>  | Register = 7Fh, T <sub>J</sub> = 25°C                                              | 1.216 | 1.235 | 1.254 | V     |

| riigilest output voltage        | VHIGH              | -40°C < T <sub>J</sub> < 125°C                                                     | 1.204 | 1.235 | 1.266 | V     |

| Output voltage step             | VSTEP              |                                                                                    |       | 5     |       | mV    |

| High-side switch on resistance  | Rhson              |                                                                                    |       | 32    |       | mΩ    |

| Low-side switch on resistance   | R <sub>LSON</sub>  |                                                                                    |       | 15    |       | mΩ    |

| UVLO rising threshold           | V <sub>UVLOR</sub> |                                                                                    |       | 2.55  | 2.7   | V     |

| UVLO hysteretic                 | Vuvlohy            |                                                                                    |       | 150   |       | mV    |

| Switching frequency             | Fsw                |                                                                                    | 0.85  |       | 2.2   | MHz   |

| Frequency variation             | Fsw                |                                                                                    |       |       | 25%   |       |

| Minimum on time (7)             | T <sub>MINON</sub> |                                                                                    |       | 60    |       | ns    |

| Switch leakage                  | Isw                | V <sub>EN</sub> = 0V, VIN = 5V, V <sub>SW</sub> = 0V and 5V, T <sub>J</sub> = 25°C |       |       | 1     | μΑ    |

| EN input current                | I <sub>EN</sub>    | V <sub>EN</sub> = 5V                                                               |       | 4     |       | μA    |

| EN logic low voltage            | V <sub>ENL</sub>   |                                                                                    |       |       | 0.4   | V     |

| EN logic high voltage           | VENH               |                                                                                    | 1.8   |       |       | V     |

| Power good UV threshold rising  | PGVth-Hi           | Good                                                                               |       | 0.9   |       | VOUT  |

| Power good UV threshold falling | PGVth-Lo           | Fault                                                                              |       | 0.85  |       | VOUT  |

| Power good OV threshold rising  | PGVth-Hi           | Fault                                                                              |       | 1.1   |       | VOUT  |

| Power good OV threshold falling | PGVth-Lo           | Good                                                                               |       | 1.05  |       | VOUT  |

| Power good pull-down voltage    | V <sub>PGL</sub>   | Isink = 1mA                                                                        |       |       | 0.4   | V     |

| Power good delay                | T <sub>PGd</sub>   |                                                                                    |       | 30    |       | μs    |

| Power good leakage              | $I_{PGd}$          |                                                                                    |       |       | 1     | μA    |

# **ELECTRICAL CHARACTERISTICS** (continued)

VIN = 5V,  $T_J$  = -40°C to +125°C <sup>(6)</sup>, typical value is tested at  $T_J$  = +25°C. The limit over temperature is guaranteed by characterization, unless otherwise noted.

| Parameter                                    | Symbol              | Condition    | Min | Тур  | Max | Units   |

|----------------------------------------------|---------------------|--------------|-----|------|-----|---------|

| VOUT OVP threshold                           |                     | Rising edge  |     | +10% |     | VTARGET |

| High-side switch peak current limit (source) | I <sub>peak</sub>   |              | 7   | 11   |     | Α       |

| High-side switch valley current limit (7)    | I <sub>valley</sub> |              |     | 5.8  |     | А       |

| Low-side switch current                      |                     | PFM mode     |     | 0    |     | Α       |

| limit (sink)                                 |                     | PWM mode (7) |     | -5   |     | Α       |

| Soft-start time                              | Tss-on              |              | 0.4 | 1    | 1.6 | ms      |

| Discharge resistor                           |                     |              |     | 500  |     | Ω       |

| Thermal warning (6)                          |                     |              |     | 130  |     | °C      |

| Thermal shutdown <sup>(6)</sup>              |                     |              |     | 150  |     | °C      |

| DAC resolution <sup>(7)</sup>                |                     |              |     | 7    |     | bits    |

#### NOTE:

<sup>6)</sup> Not tested in production, guaranteed by over-temperature correlation.

<sup>7)</sup> Guaranteed by engineering sample characterization.

# I/O LEVEL CHARACTERISTICS

| Parameter                                                                      | Symbol           | Condition                                                                                | HS-                | Mode                  | LS-                | Units                 |       |

|--------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------|--------------------|-----------------------|--------------------|-----------------------|-------|

| Parameter                                                                      | Symbol           | Condition                                                                                | Min                | Max                   | Min                | Max                   | Units |

| Low-level input voltage                                                        | $V_{IL}$         |                                                                                          | -0.5               | 0.3Vcc                | -0.5               | 0.3Vcc                | V     |

| High-level input voltage                                                       | V <sub>IH</sub>  |                                                                                          | 0.7V <sub>CC</sub> | V <sub>CC</sub> + 0.5 | 0.7V <sub>CC</sub> | V <sub>CC</sub> + 0.5 | V     |

| Hysteresis of Schmitt                                                          | $V_{HYS}$        | Vcc > 2V                                                                                 | 0.05Vcc            | -                     | 0.05Vcc            | -                     | V     |

| trigger inputs                                                                 |                  | Vcc < 2V                                                                                 | 0.1Vcc             | -                     | 0.1Vcc             | -                     |       |

| Low-level output voltage (open drain) at 3mA sink                              | Vol              | Vcc > 2V                                                                                 | 0                  | 0.4                   | 0                  | 0.4                   | V     |

| current                                                                        | VOL              | Vcc < 2V                                                                                 | 0                  | 0.2Vcc                | 0                  | 0.2Vcc                | v     |

| Low-level output current                                                       | I <sub>OL</sub>  |                                                                                          | -                  | 3                     | -                  | 3                     | mA    |

| Transfer gate on resistance for currents between SDA and SCAH, or SCL and SCLH | R <sub>onL</sub> | VOL level, IOL = 3mA                                                                     | -                  | 50                    | -                  | 50                    | Ω     |

| Transfer gate on resistance between SDA and SCAH, or SCL and SCLH              | $R_{onH}$        | Both signals (SDA and SDAH, or SCL and SCLH) at Vcc level                                | 50                 | -                     | 50                 | -                     | kΩ    |

| Pull-up current of the SCLH current source                                     | I <sub>cs</sub>  | SCLH output levels between 0.3V <sub>CC</sub> and 0.7V <sub>CC</sub>                     | 2                  | 6                     | 2                  | 6                     | mA    |

| Rise time of the SCLH                                                          | trCL             | Output rise time (current source enabled) with an external pull-up current source of 3mA |                    |                       |                    |                       |       |

| or SCL signal                                                                  | HOL              | Capacitive load from 10pF to 100pF                                                       | 10                 | 40                    |                    |                       | ns    |

|                                                                                |                  | Capacitive load of 400pF                                                                 | 20                 | 80                    |                    |                       | ns    |

| Fall time of the SCLH or                                                       | t <sub>fCL</sub> | Output fall time (current source enabled) with an external pull-up current source of 3mA |                    |                       |                    |                       |       |

| SCL signal                                                                     |                  | Capacitive load from 10pF to 100pF                                                       | 10                 | 40                    |                    |                       | ns    |

|                                                                                |                  | Capacitive load of 400pF                                                                 | 20                 | 80                    | 20                 | 250                   | ns    |

| Rise time of SDAH                                                              | $t_{rDA}$        | Capacitive load from 10pF to 100pF                                                       | 10                 | 80                    | -                  | -                     | ns    |

| signal                                                                         |                  | Capacitive load of 400pF                                                                 | 20                 | 160                   | 20                 | 250                   | ns    |

| Fall time of SDAH signal                                                       | <b>t</b> fDA     | Capacitive load from 10pF to 100pF                                                       | 10                 | 80                    | -                  | -                     | ns    |

|                                                                                |                  | Capacitive load of 400pF                                                                 | 20                 | 160                   | 20                 | 250                   | ns    |

| Input current for each I/O pin                                                 | l <sub>i</sub>   | Input voltage between 0.1Vcc and 0.9Vcc                                                  | -                  | 10                    | -10                | +10                   | μΑ    |

| Capacitance for each I/O pin                                                   | Ci               |                                                                                          | -                  | 10                    | -                  | 10                    | pF    |

# I<sup>2</sup>C PORT SIGNAL CHARACTERISTICS

| Danamatan                                                                              | Comple at           | Com dition                             | Cb = | 100pF  | Cb = 40            | Units |       |

|----------------------------------------------------------------------------------------|---------------------|----------------------------------------|------|--------|--------------------|-------|-------|

| Parameter                                                                              | Symbol              | Condition                              | Min  | Max    | Min                | Max   | Units |

| SCLH and SCL clock frequency                                                           | f <sub>SCHL</sub>   |                                        | 0    | 3.4    | 0                  | 0.4   | MHz   |

| Set-up time for a repeated start condition                                             | T <sub>SU;STA</sub> |                                        | 160  | -      | 600                | ı     | ns    |

| Hold time (repeated) start condition                                                   | T <sub>HD;STA</sub> |                                        | 160  | -      | 600                | 1     | ns    |

| Low period of the SCL clock                                                            | t <sub>LOW</sub>    |                                        | 160  | -      | 1300               | -     | ns    |

| High period of the SCL clock                                                           | tніgн               |                                        | 60   | -      | 600                | -     | ns    |

| Data set-up time                                                                       | T <sub>SU:DAT</sub> |                                        | 10   | -      | 100                | 1     | ns    |

| Data hold time                                                                         | T <sub>HD;DAT</sub> |                                        | 0    | 70     | 0                  | -     | ns    |

| Rise time of SCLH signal                                                               | trCL                |                                        | 10   | 40     | 20*0.1Cb           | 300   | ns    |

| Rise time of SCLH signal after a repeated start condition and after an acknowledge bit | t <sub>fCL1</sub>   |                                        | 10   | 80     | 20*0.1Cb           | 300   | ns    |

| Fall time of SCLH signal                                                               | T <sub>fCL</sub>    |                                        | 10   | 40     | 20*0.1Cb           | 300   | ns    |

| Rise time of SDAH signal                                                               | t <sub>fDA</sub>    |                                        | 10   | 80     | 20*0.1Cb           | 300   | ns    |

| Fall time of SDAH signal                                                               | T <sub>fDA</sub>    |                                        | 10   | 80     | 20*0.1Cb           | 300   | ns    |

| Set-up time for a stop condition                                                       | T <sub>SU;STO</sub> |                                        | 160  | -      | 600                | -     | ns    |

| Bus free time between a stop and start condition                                       | T <sub>BUF</sub>    |                                        | 160  | -      | 1300               | -     | ns    |

| Data valid time                                                                        | T <sub>VD;DAT</sub> |                                        | -    | 16     | -                  | 90    | ns    |

| Data valid acknowledge time                                                            | T <sub>VD;ACK</sub> |                                        | -    | 160    | -                  | 900   | ns    |

| Canaditive land for each                                                               |                     | SDAH and SCLH line                     | -    | 100    | -                  | 400   | pF    |

| Capacitive load for each bus line                                                      | Сь                  | SDAH + SDA line and<br>SCLH + SCL line | -    | 400    | -                  | 400   | pF    |

| Noise margin at the low level                                                          | V <sub>n</sub> L    | For each connected device              | -    | 0.1Vcc | 0.1Vcc             | -     | ٧     |

| Noise margin at the high level                                                         | V <sub>n</sub> H    | For each connected device              | -    | 0.2Vcc | 0.2V <sub>CC</sub> | -     | V     |

**NOTE:**  $V_{CC}$  is the  $I^2C$  bus voltage in the 1.5V to 3.3V range.

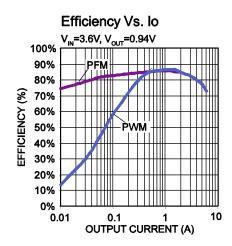

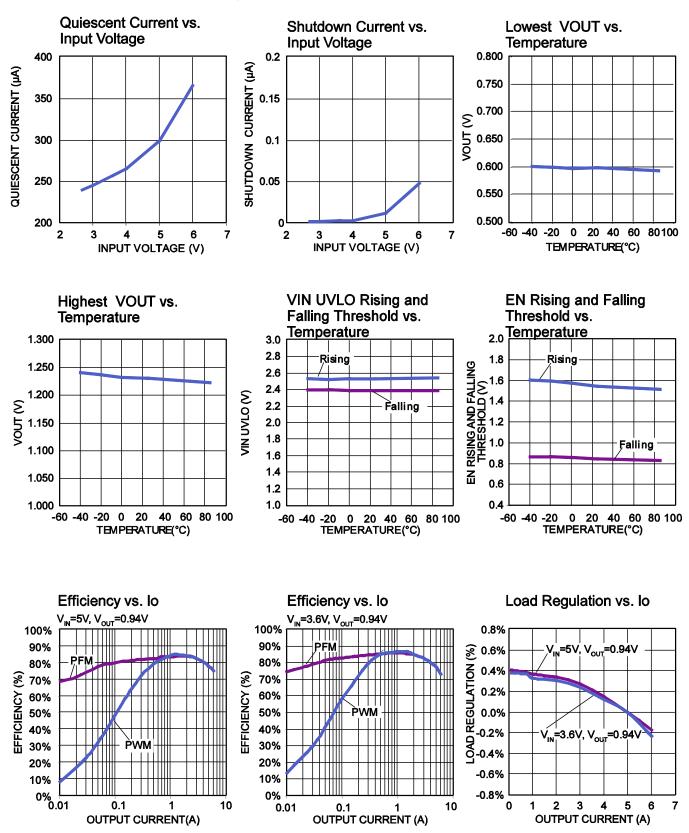

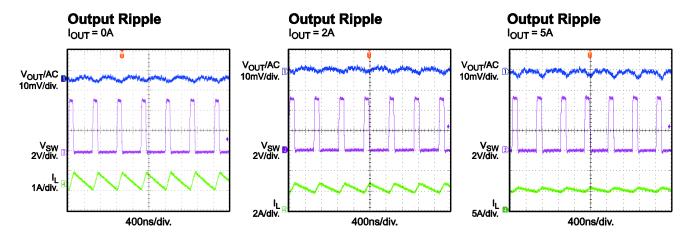

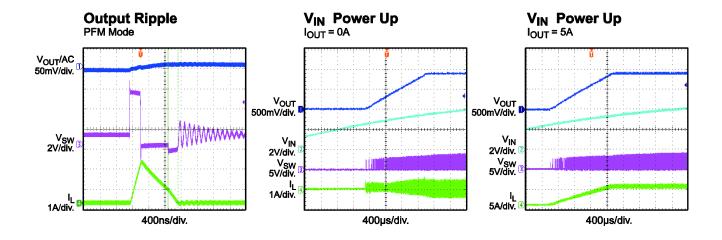

# TYPICAL CHARACTERISTICS

VIN = 5V, VOUT = 0.94V, L = 0.47 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

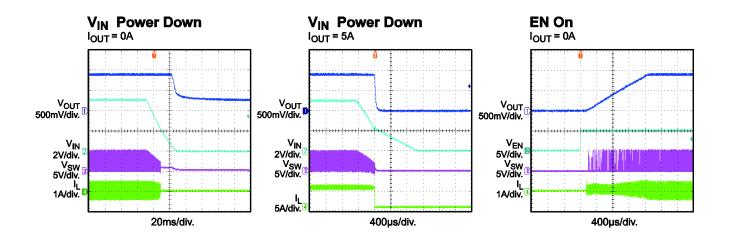

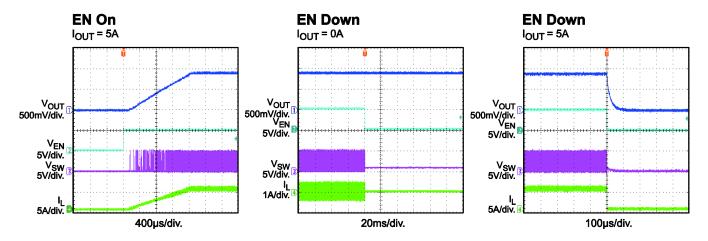

# TYPICAL CHARACTERISTICS (continued)

VIN = 5V, VOUT = 0.94V, L = 0.47 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (continued)**

VIN = 5V, VOUT = 0.94V, L = 0.47 $\mu$ H,  $T_A$  = 25°C, unless otherwise noted.

# **PIN FUNCTIONS**

| Package<br>Pin # | Name | Description                                                 |

|------------------|------|-------------------------------------------------------------|

| 1                | PG   | Power good output.                                          |

| 2                | SDA  | I <sup>2</sup> C serial data.                               |

| 3, thermal pad   | GND  | Power ground.                                               |

| 4, 5, 6          | VIN  | Input supply voltage.                                       |

| 7, 8, 9          | SW   | Switch note.                                                |

| 10               | EN   | On and off control.                                         |

| 11               | AGND | Analog ground.                                              |

| 12               | VOUT | Output voltage sensing.                                     |

| 13               | SCL  | I <sup>2</sup> C serial clock.                              |

| 14               | AVIN | Analog input supply voltage and multi-usage of P3 function. |

# **REGISTERS AND DESCRIPTION**

# **Register Map**

| ADD | NAME        | R/W   | D7                  | D6                              | D5    | D4      | D3                 | D2    | D1     | D0   |

|-----|-------------|-------|---------------------|---------------------------------|-------|---------|--------------------|-------|--------|------|

| 00  | Status      | R     | ILIM                | UVLO                            | OVP   | VoOV    | VoUV               | PGOOD | OTW    | EN   |

| 00  | Status      | N.    | ILIIVI              | ILIM   OVEO   OVI   VOOV   VOOV | VUOV  | V       | FGOOD              | 010   | stat   |      |

| 01  | VSEL        | R/W   | EN                  |                                 |       | Out     | out referer        | ice   |        |      |

| 02  | SysCntlreg1 | R/W   | Switching frequency |                                 |       |         | Transient response |       | Vinovp | Mode |

| 03  | SyoCattrog? | R/W   | Poor                | anuad                           | Go    | Out-dis | GI filt            | Slew  | P3     | P3   |

| 03  | SysCntlreg2 | IX/VV | Reserved            |                                 | 9     | Out-uis | 5_111              | rate  | Enable | Set  |

| 04  | ID1         | R     | Vendor ID           |                                 |       |         |                    | Die I | D      |      |

| 05  | ID2         | R     |                     | Rese                            | erved |         |                    | Die r | ev     |      |

NOTE: The burst write cannot be on Reg 03.

# **Default Value of Registers**

| ADD | NAME        | R/W | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 00  | Status      | R   | N/A |

| 01  | VSEL        | R/W | 1   | 1   | 0   | 0   | 0   | 1   | 0   | 0   |

| 02  | SysCntlreg1 | R/W | 1   | 0   | 0   | 0   | 1   | 1   | 0   | 0   |

| 03  | SysCntlreg2 | R/W | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   |

| 04  | ID1         | R   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   |

| 05  | ID2         | R   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

# **Register Description**

# 1. Reg00 Status

| NAME    | BITS | DESCRIPTION                                                                                |

|---------|------|--------------------------------------------------------------------------------------------|

| ILIM    | D7   | When the bit is high, IC is in the current limit.                                          |

| UVLO    | D6   | When the bit is high, VIN is less than the UVLO threshold.                                 |

| OVP     | D5   | When the bit is high, VIN is greater than the OVP threshold.                               |

| VoOV    | D4   | When the bit is high, a voltage higher than 110% of the regulation voltage is presented.   |

| VoUV    | D3   | When the bit is high, a voltage lower than 90% of the regulation voltage is presented.     |

| PGOOD   | D2   | When the bit is high, the output is in regulation; otherwise, the output voltage is out of |

| FGOOD   | DZ   | the ±10% regulation window.                                                                |

| OTW     | D1   | When the junction temperature is higher than 130°C, the bit is high; otherwise, the bit    |

| OTVV    | Di   | is low.                                                                                    |

| En Stat | D0   | When the bit is high, the SMPS is enabled; when the bit is low, the SMPS is disabled.      |

# 2. Reg01 VSEL

| NAME                | BITS   | DESCRIPTION                                                                                                       |

|---------------------|--------|-------------------------------------------------------------------------------------------------------------------|

| EN                  | D7     | I <sup>2</sup> C controlled enable. When EN is low, the converter is off. When EN is high, the EN bit takes over. |

| Output<br>Reference | D[6:0] | Sets the output voltage from 0.6V to 1.235V (see Table 1).                                                        |

# NOT RECOMMENDED FOR NEW DESIGNS, REFER TO MP8847 Table 1: Output Voltage Chart

| Table 1. Output Voltage Chart |       |          |       |          |       |          |       |

|-------------------------------|-------|----------|-------|----------|-------|----------|-------|

| D[6:0]                        | VOUT  | D[6:0]   | VOUT  | D[6:0]   | VOUT  | D[6:0]   | VOUT  |

| 000 0000                      | 0.600 | 010 0000 | 0.760 | 100 0000 | 0.920 | 110 0000 | 1.080 |

| 000 0001                      | 0.605 | 010 0001 | 0.765 | 100 0001 | 0.925 | 110 0001 | 1.085 |

| 000 0010                      | 0.610 | 010 0010 | 0.770 | 100 0010 | 0.930 | 110 0010 | 1.090 |

| 000 0011                      | 0.615 | 010 0011 | 0.775 | 100 0011 | 0.935 | 110 0011 | 1.095 |

| 000 0100                      | 0.620 | 010 0100 | 0.780 | 100 0100 | 0.940 | 110 0100 | 1.100 |

| 000 0101                      | 0.625 | 010 0101 | 0.785 | 100 0101 | 0.945 | 110 0101 | 1.105 |

| 000 0110                      | 0.630 | 010 0110 | 0.790 | 100 0110 | 0.950 | 110 0110 | 1.110 |

| 000 0111                      | 0.635 | 010 0111 | 0.795 | 100 0111 | 0.955 | 110 0111 | 1.115 |

| 000 1000                      | 0.640 | 010 1000 | 0.800 | 100 1000 | 0.960 | 110 1000 | 1.120 |

| 000 1001                      | 0.645 | 010 1001 | 0.805 | 100 1001 | 0.965 | 110 1001 | 1.125 |

| 000 1010                      | 0.650 | 010 1010 | 0.810 | 100 1010 | 0.970 | 110 1010 | 1.130 |

| 000 1011                      | 0.655 | 010 1011 | 0.815 | 100 1011 | 0.975 | 110 1011 | 1.135 |

| 000 1100                      | 0.660 | 010 1100 | 0.820 | 100 1100 | 0.980 | 110 1100 | 1.140 |

| 000 1101                      | 0.665 | 010 1101 | 0.825 | 100 1101 | 0.985 | 110 1101 | 1.145 |

| 000 1110                      | 0.670 | 010 1110 | 0.830 | 100 1110 | 0.990 | 110 1110 | 1.150 |

| 000 1111                      | 0.675 | 010 1111 | 0.835 | 100 1111 | 0.995 | 110 1111 | 1.155 |

| 001 0000                      | 0.680 | 011 0000 | 0.840 | 101 0000 | 1.000 | 111 0000 | 1.160 |

| 001 0001                      | 0.685 | 011 0001 | 0.845 | 101 0001 | 1.005 | 111 0001 | 1.165 |

| 001 0010                      | 0.690 | 011 0010 | 0.850 | 101 0010 | 1.010 | 111 0010 | 1.170 |

| 001 0011                      | 0.695 | 011 0011 | 0.855 | 101 0011 | 1.015 | 111 0011 | 1.175 |

| 001 0100                      | 0.700 | 011 0100 | 0.860 | 101 0100 | 1.020 | 111 0100 | 1.180 |

| 001 0101                      | 0.705 | 011 0101 | 0.865 | 101 0101 | 1.025 | 111 0101 | 1.185 |

| 001 0110                      | 0.710 | 011 0110 | 0.870 | 101 0110 | 1.030 | 111 0110 | 1.190 |

| 001 0111                      | 0.715 | 011 0111 | 0.875 | 101 0111 | 1.035 | 111 0111 | 1.195 |

| 001 1000                      | 0.720 | 011 1000 | 0.880 | 101 1000 | 1.040 | 111 1000 | 1.200 |

| 001 1001                      | 0.725 | 011 1001 | 0.885 | 101 1001 | 1.045 | 111 1001 | 1.205 |

| 001 1010                      | 0.730 | 011 1010 | 0.890 | 101 1010 | 1.050 | 111 1010 | 1.210 |

| 001 1011                      | 0.735 | 011 1011 | 0.895 | 101 1011 | 1.055 | 111 1011 | 1.215 |

| 001 1100                      | 0.740 | 011 1100 | 0.900 | 101 1100 | 1.060 | 111 1100 | 1.220 |

| 001 1101                      | 0.745 | 011 1101 | 0.905 | 101 1101 | 1.065 | 111 1101 | 1.225 |

| 001 1110                      | 0.750 | 011 1110 | 0.910 | 101 1110 | 1.070 | 111 1110 | 1.230 |

| 001 1111                      | 0.755 | 011 1111 | 0.915 | 101 1111 | 1.075 | 111 1111 | 1.235 |

# 3. Reg02 SysCntlreg1

| NAME                   | BITS   | DESCRIPTION                                                                          |                                                   |                   |                           |  |  |

|------------------------|--------|--------------------------------------------------------------------------------------|---------------------------------------------------|-------------------|---------------------------|--|--|

|                        |        | D[7:5]                                                                               | Switching Frequency                               | D[7:5]            | Switching Frequency       |  |  |

| Curitobina             |        | 000 2.2MHz 100 1.25MHz (                                                             |                                                   | 1.25MHz (default) |                           |  |  |

| Switching<br>Frequency | D[7:5] | 001                                                                                  | 2MHz                                              | 101               | 1.11MHz                   |  |  |

| riequency              |        | 010                                                                                  | 1.67MHz                                           | 110               | 0.85MHz                   |  |  |

|                        |        | 011                                                                                  |                                                   | 111               |                           |  |  |

| Transient              | D[4:3] | D[4:3]                                                                               | Response Speed                                    | D[4:3]            | Response Speed            |  |  |

| Response               |        | 00                                                                                   | Ultra-fast                                        | 01                | Fast (default)            |  |  |

| Response               |        | 10                                                                                   | Normal                                            | 11                | Slow                      |  |  |

|                        |        |                                                                                      |                                                   |                   | xcursion of Vo from the   |  |  |

| PG_LOHI                | D2     |                                                                                      |                                                   | both a positive a | and negative excursion of |  |  |

|                        |        | Vo from the reference.                                                               |                                                   |                   |                           |  |  |

| VIN OVP                | D1     | A "1" disables the VIN OVP function. The converter continues operating. A "0" (defau |                                                   |                   |                           |  |  |

| VIIN_OVE               | וט     | turns off the conver                                                                 | turns off the converter when VIN reaches VIN MAX. |                   |                           |  |  |

| Mode                   | D0     | A "0" enables PFM                                                                    | mode; a high disables PF                          | M mode.           |                           |  |  |

# 4. Reg03 SysCntlreg2

| NAME      | BITS   | DESCRIPTION                                  |                       |                          |                            |

|-----------|--------|----------------------------------------------|-----------------------|--------------------------|----------------------------|

| Reserved  | D[7:6] | Reserved.                                    |                       |                          |                            |

| Go        | D5     | Writing to this bit sta                      | arts a VOUT transitio | n regardless of its init | tial value.                |

| Output    | D4     | A "0" disables the                           | output discharge. T   | he output voltage mi     | ust be discharged by the   |

| Discharge | D4     | load. A high enables the internal pull-down. |                       |                          |                            |

| GI_filt   | D3     | A "0" disables the PG delay.                 |                       |                          |                            |

| Slew Rate | D2     | D2                                           | Slew Rate             | D2                       | Slew Rate                  |

| Siew Rate |        | 0                                            | 32mV/µs               | 1                        | 8mV/µs                     |

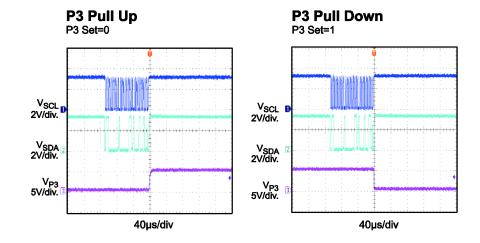

| P3 Enable | D1     | A "1" enables the P                          | 3 set function. Only  | a "1" can make the P     | 3 Set bit control the AVIN |

| voltage.  |        |                                              |                       |                          |                            |

| P3 Set    | D0     | When the P3 Enab                             | le bit = 1, the AVIN  | voltage is pulled high   | if P3 Set = 0; otherwise,  |

| F 3 3et   | D0     | the AVIN voltage is                          | pulled low.           |                          |                            |

# 5. Reg04 ID1

| NAME      | BITS   | DESCRIPTION |

|-----------|--------|-------------|

| Vendor ID | D[7:4] | Vendor ID.  |

| Die ID    | D[3:0] | IC type.    |

# 6. Reg05 ID2

| NAME     | BITS   | DESCRIPTION   |

|----------|--------|---------------|

| Reserved | D[7:4] | Reserved.     |

| Die Rev  | D[3:0] | Die revision. |

# **Operation Status**

| CONDITION                                    | PG   | REGULATION | LATCH-OFF | STATUS BIT |

|----------------------------------------------|------|------------|-----------|------------|

| VIN over-voltage                             | Low  | Off        | No        | OVP        |

| VIN under-voltage                            | Low  | Off        | N/A       | UVLO       |

| Thermal warning                              | Low  | On         | No        | OTW        |

| Thermal shutdown                             | Low  | Off        | Yes       | N/A        |

| Current limit                                | High | On         | No        | ILIM       |

| Output under-voltage                         | Low  | Off        | Yes       | VoUV       |

| Output over voltage (>110% of target output) | Low  | On         | No        | VoOV       |

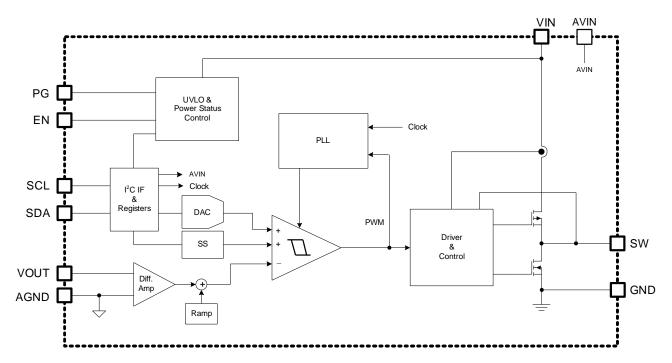

# **BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

# **OPERATION**

The MP8848 is a low-voltage, 6A, synchronous, step-down converter with a controllable I<sup>2</sup>C interface. The MP8848 applies MPS's patented constant-frequency hysteretic control to utilize fast transient response of the hysteretic control and keep the switching frequency constant. No compensation is required, which simplifies the design procedure.

The MP8848 integrates an I<sup>2</sup>C-compatible interface that allows transfers of up to 3.4Mbps. This communication interface can be used for dynamic voltage scaling with voltage steps down to 5mV with the output voltage from 0.6V to 1.235V. The voltage transition slew rate can be controlled as well.

#### **Light-Load Operation**

In light-load condition, the MP8848 uses a proprietary control scheme to save power and improve efficiency. The MP8848 turns off the low-side switch when the inductor current begins reversing. The MP8848 then works in discontinuous conduction mode (DCM) operation.

#### Enable (EN)

When the input voltage is greater than the under-voltage lockout (UVLO) threshold (typically 2.55V), the MP8848 can be enabled by pulling EN above 1.8V. Pull EN down to ground to disable the MP8848. The IC can also be disabled by floating EN. There is an internal  $1M\Omega$  resistor from EN to ground.

#### Soft Start (SS)

The MP8848 has a built-in soft start that ramps up the output voltage at a controlled slew rate, preventing inrush current and output voltage overshoot at start-up. The soft-start time is about 1ms.

#### **Power Good (PG) Indicator**

The MP8848 has an open-drain output for power good (PG) indication. When the output voltage is within ±10% of the regulation voltage, PG is pulled up to VIN by the external resistor.

#### **Current Limit**

The MP8848 has a typical 11A current limit for the high-side switch. When the high-side switch reaches the current limit, the MP8848 expands the minimum off time until the current drops to 5.8A before the high-side switch is turned on for the next switching cycle. This prevents the inductor current from continuing to build up and damaging the components.

#### **Thermal Protection**

The MP8848 employs thermal shutdown by monitoring the junction temperature of the IC internally. If the junction temperature exceeds the thermal warning threshold (around 130°C), OTW is set. If there is no action or response from the system, the junction temperature continues rising until it exceeds the thermal shutdown threshold (typically 150°C). After thermal shutdown, a new power start-up cycle is needed to turn on the MP8848 again.

# I<sup>2</sup>C INTERFACE

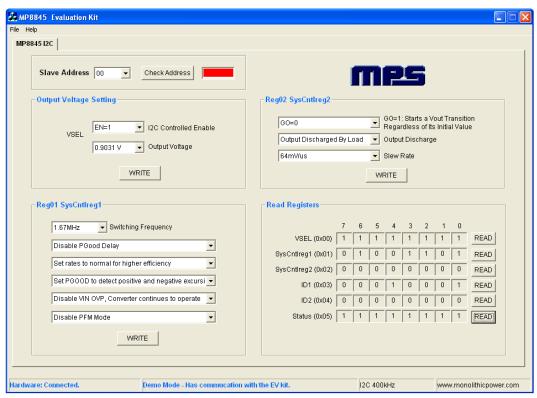

The MP8848 can communicate with the core and the I<sup>2</sup>C for smart design. MPS has a GUI control interface (see Figure 2). The installation process and usage can be found in the MP884x Family Software Guide.

### I<sup>2</sup>C Address

The I<sup>2</sup>C slave address of the MP8848 is 0xC0H/0xC1H internally (see Table 2). If other slave addresses are needed, please contact the factory.

Table 2: I<sup>2</sup>C Slave Address

| Hex              | A7   | A6 | A5 | A4 | A3 | A2 | A1 | A0  |

|------------------|------|----|----|----|----|----|----|-----|

| W 0xC0<br>R 0xC1 | 1    | 1  | 0  | 0  | 0  | 0  | 0  | R/W |

| Address          | 0x60 |    |    |    |    |    |    |     |

#### I<sup>2</sup>C Enable

The MP8848's EN pin can start up and shut down the converter, and the  $I^2C$  EN pin can control the converter as well. The Reg01 VSEL D7 bit is  $I^2C$ -controlled enabled. When writing D7 = 0, the converter is off. When writing D7 = 1, the converter is on. Both the external EN and  $I^2C$  EN can control the converter. The converter works only when both EN pins are high.

#### **Output Voltage Select**

The MP8848 output voltage is I<sup>2</sup>Cprogrammable. There is no need to set feedback resistors to achieve different output voltages. The default output voltage is 0.94V but can be set from 0.6V to 1.235V in 5mV steps via the I<sup>2</sup>C. To change the output voltage. write the Go bit (Reg03 Syscntlreg2 [D5]) to 1. This action means that the output voltage can be set to another value that is not the default Vo voltage. Then write the Output Reference bit (Reg01 VSEL [D6:D0]). The output voltage can be changed according to Table 1.

To guarantee a normal output voltage, the input voltage is suggested to be 1.5V higher than the pre-set output voltage.

#### **Switching Frequency**

The default switching frequency of the MP8848 is 1.25MHz. However, the frequency can also be changed based on the application. By writing the Switching Frequency bits (Reg02 SysCntlreg1 [D7:D5], the switching frequency can be programmed to one of six possible values. Their corresponding data can be found in Reg02 SysCntlreg1.

Figure 2: MP884x Family Control Interface

#### **PG** Configuration

The MP8848 has an option to use the PG\_LOHI function. This function can be written in the PG\_LOHI bit (Reg02 Syscntlreg1 [D2]). The default value is 1, where PG senses both a positive and negative excursion of Vo from the reference. If writing this bit to 0, PG only senses a negative voltage excursion of Vo from the reference.

# **Input Over-Voltage Protection (OVP)**

The MP8848 has an option to use the VIN\_OVP function. This function can be written in the VIN\_OVP bit (Reg02 Syscntlreg1 [D1]). The default value is 0, where the VIN\_OVP function is enabled. When VIN is higher than 6.3V, the converter is disabled. After VIN recovers to 6.2V, the converter restarts. If the VIN\_OVP bit is set to 1, VIN OVP is disabled. The converter will not stop, even if VIN exceeds its safe range.

#### **Forced Continuous Conduction Mode (CCM)**

The MP8848 has auto-pulse-frequency modulation (PFM) mode and forced continuous conduction mode (CCM). This function can be written in the Mode bit (Reg02 Syscntlreg1 [D0]). The default value is 0, where auto-PFM mode is selected. Considering a smaller Vo ripple and regulation for a full load range, forced CCM is recommended. Set this bit to 1 to disable PFM mode.

#### **Output Discharge**

The MP8848 has an output discharge function. Writing the Out-dis bit (Reg03 SysCntlreg2 [D4]) can change the output discharge mode. The default value is 1. Discharge the internal Vo resistance when EN is low. Writing D4 = 1 can enable the function, and then the output voltage can be discharged by the internal pull-down resistance.

# **Output Voltage Transition Slew Rate**

When the output voltage switches from low to high or from high to low, the transition slew rate can differ. There are two possible values for selection. Through writing the Slew Rate bits (Reg03 Syscntlreg2 D2), the transition slew rate can be set at one possible value based on the application. The internal reference follows the set slew rate, but the output voltage slew rate does not always follow the internal reference. Considering the output capacitor and inductor, the actual output voltage slew rate should be a little slower.

#### **AVIN Multi-Use**

The MP8848's AVIN pin has multi-usage. When the P3 Enable bit (Reg03 SysCntlreg2 D1) is 0, AVIN is an internal analog supply. When the P3 Control bit (Reg03 sysCntlrge2 D1) is 1, the P3 voltage is controlled by the P3 Set bit (Reg03 sysCntlrge2 D0). The P3 voltage is high if D0 = 0; otherwise, the P3 voltage is low (see Table 3).

Table 3: AVIN Multi-Use

| D1 | D0 | AVIN                   |

|----|----|------------------------|

| 0  | 0  | Internal analog gupply |

| 0  | 1  | Internal analog supply |

| 1  | 0  | Forced to 1            |

| 1  | 1  | Forced to 0            |

### I<sup>2</sup>C Register Hold On

The MP8848 has a special function: the I<sup>2</sup>C register can hold on after EN changes low. The updated register can be held for later application conditions, even if the external EN pulls low.

# TYPICAL APPLICATION CIRCUITS

Figure 3: Application Circuit

# **PACKAGE INFORMATION**

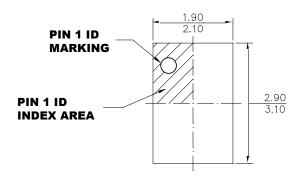

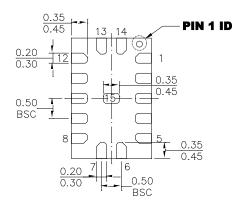

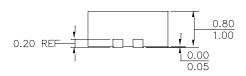

# QFN-15 (2mmx3mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

### **NOTE:**

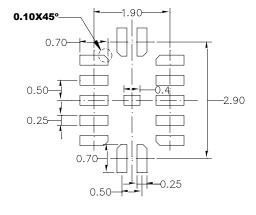

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

- 3) JEDEC REFERENCE IS MO-220.

- 4) DRAWING IS NOT TO SCALE.

#### **RECOMMENDED LAND PATTERN**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.