大电流应用的多相变换器设计

每月为您发送最具参考价值的行业文章

我们会保障您的隐私

简介

为高端现场可编程门阵列(FPGA)和专用集成电路(ASIC)核心轨供电,不仅需要大电流,还必须实现精准的瞬态控制。近几年来,FPGA、ASIC 及其相关系统快速发展,复杂程度不断提高,其供电系统规范也随之做出了重大改变。设计人员在设计供电系统时,需要在效率、动态响应以及 MOSFET 尺寸与功耗之间进行审慎的权衡。

为满足这些严苛要求,最常用的解决方案是采用并联电源架构。该方案可以在多个电源(各相)之间实现均流,从而更轻松、更高效地提供所需功率。各电源支路之间还可以设置相位差,以进一步提高性能,从而降低总电流和电压纹波。但该方案需确保相位均匀分布,且所有相电流保持均衡,因此设计过程较为复杂。

为了满足 FPGA 和 ASIC 核心轨的低电压、大电流需求,同时实现精准瞬态控制,电源系统现在均采用多相电源解决方案来实现更高频率的运行。

MPS的 MPM3698 和 MPM3699 等电源模块均采用自动交错和切相等先进的多相控制方法。本文将介绍多相变换器的设计流程,并阐明多相电源设计的关键因素。

FPGA 和 ASIC 设计要求

在FPGA 和 ASIC 电源设计中,需要考量的最重要参数之一就是不同电源轨的电压要求。对于 FPGA 和 ASIC 中的通用电压轨,输入电压 (VIN) 默认值为12V,输出电流 (ITDC) 为180A,输出电压 (VOUT) 为1.2V。表1罗列了常见 FPGA 的电压要求(本文以 Spartan 7 FPGA 为例)。

表1:Spartan-7 FPGA 的推荐工作条件(1)

| 符号 | 描述 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| FPGA逻辑 | |||||

| Vccint | 内部供电电压 | 0.95 | 1 | 1.05 | V |

| 内部供电电压(可选) | 0.92 | 0.95 | 0.98 | V | |

| Vccaux | 辅助供电电压 | 1.71 | 1.8 | 1.89 | V |

| Vccbram | Block RAM供电电压 | 0.95 | 1 | 1.05 | V |

| Block RAM 供电电压(可选) | 0.92 | 0.95 | 0.98 | V | |

| Vcco | HR I/O bank供电电压 | 1.14 | 3.465 | V | |

| Vin | I/O输入电压 | -0.2 | - | VCC + 0.2 | V |

| I/O输入电压(可选) | -0.2 | - | +2.625 | V | |

| Iin | 任意(供电或未供电)引脚上的最大电流 | - | - | 10 | mA |

| XADC | |||||

| Vccadc | XADC电源(以GNDADC为参考地) | 1.71 | 1.8 | 1.89 | V |

| Vrefp | 外部参考电压 | 1.2 | 1.25 | 1.3 | V |

注:

1) 该表信息来自 Mouser 的 Spartan-7 FPGAs 数据手册:DC/AC 开关特性。

表2列出了目前市场上不同FPGA的核心/辅助电压和输入/输出电压信息。表中数据取自第1列中不同FPGA型号对应的数据手册。

表2:通用 FPGA 比较(2)

| FPGA 型号 | 核心电压范围(容差)(V) | 辅助电压范围(容差)(V) | I/O电压范围(容差)(V) |

|---|---|---|---|

| Spartan - 7 | 1.0 (50mV) - 5% | 1.8 (5%) | 1.2 to 3.3 (5%) |

| Spartan - 7 (-1LI) | 0.95 (30mV) - 3% | 1.8 (5%) | 1.2 to 3.3 (5%) |

| Artix - 7 | 1.0 (50mV) - 5% | 1.8 (5%) | 1.2 to 3.3 (5%) |

| Artix - 7 (-2LE) | 0.9 (30mV) - 5% | 1.8 (5%) | 1.2 to 3.3 (5%) |

| Kintex - 7 (-2LI) | 0.95 (20mV) - 3% | 1.8 (5%) | 1.2 to 3.3 (5%) |

注:

2) 该表信息来自《电力电子新闻》文章:《为您的 FPGA 应用供电》。

两张表格均表明:现代电源设计必须满足严格的电压调节要求,在大多数情况下容差需控制在±3%左右。实现这一精度要求的可行方案之一,便是采用多相电源架构。

多相供电法

系统的基频会随所用相数成倍增加,这会提高输出端的纹波频率,从而在更小电路板面积和更低输出电容条件下实现更高的电流输出能力。

用于ASIC 和 FPGA 应用的降压变换器必须具备快速瞬态响应能力,从而能快速将能量从输入端传输到输出端。采用多相并联的变换器为负载供电,各支路以均等相位差工作,可有效降低稳态电压纹波和输入/输出 RMS 电流,从而减少对输入输出电容的需求。

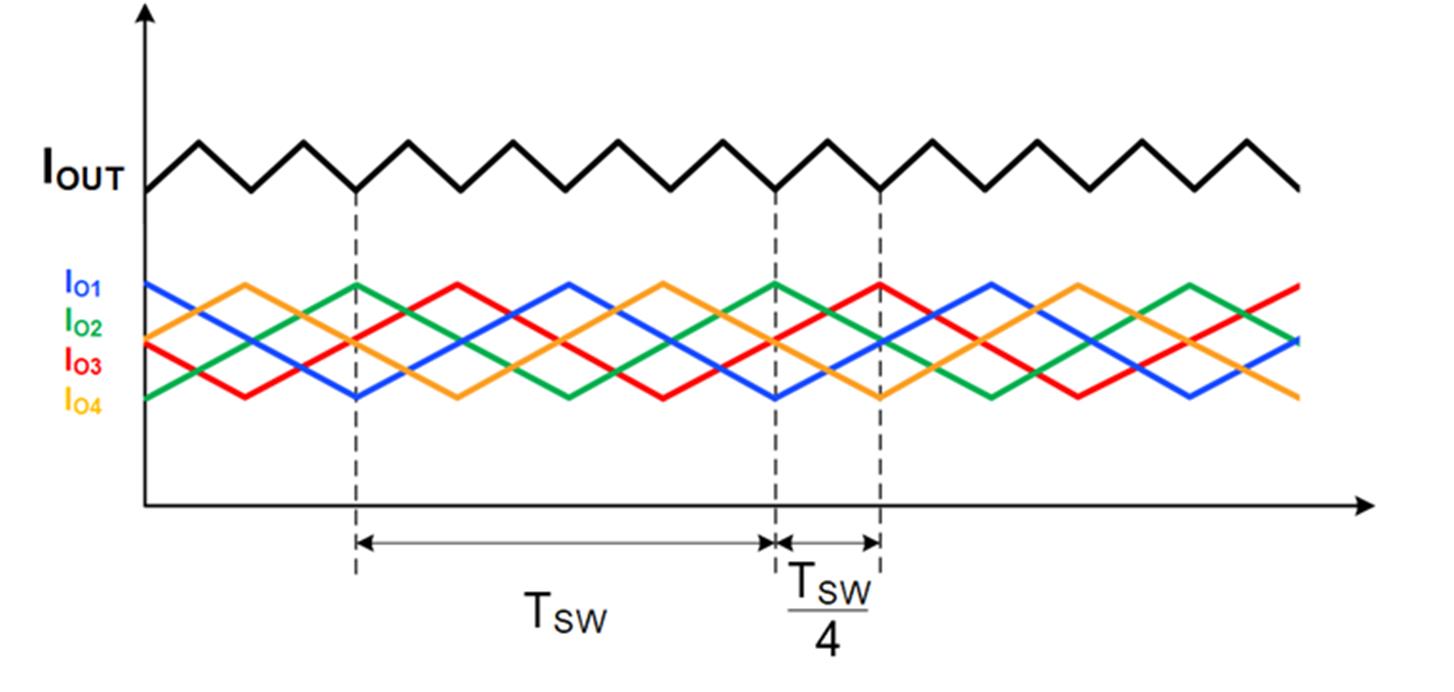

采用该方案可有效降低电流纹波并减小电感,同时还能抑制瞬态电压尖峰。根据频率倍增效应,纹波幅值将降低为1/N(N为相数),而纹波频率则提升至N倍。以4相架构为例:总电感电流纹波(IOUT = IO1 + IO2 + IO3 + IO4)幅值仅为单相模式的1/4,纹波频率则达到单相的4倍(见图1)。

图1:4相应用的总电流纹波

多相变换器面临的挑战

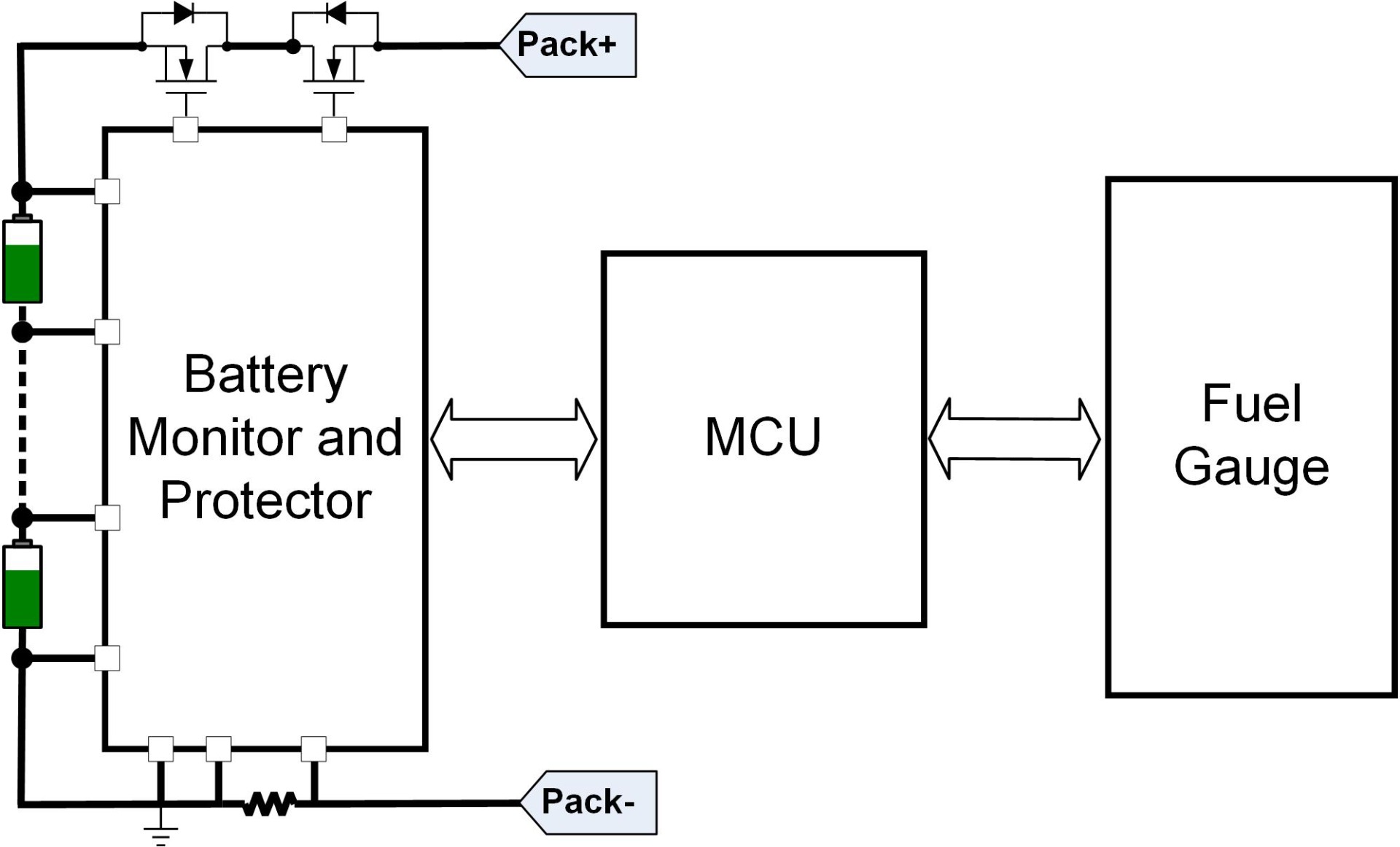

采用多相变换器是实现高功率输出与超快响应速度的关键。但在FPGA和ASIC等应用中,系统功耗往往存在大幅波动。MPS为此提供了分立式与模块化两种解决方案。模块化方案设计更简便,占板面积更小;相比分立式方案,该方案仅由三个DrMOS、一个控制器及三个电感组成,因此可显著降低系统复杂度。例如,在峰值运算负载下,输出电流需求可骤增至100A;而在空载或低负载时段,电流又会急剧下降至10A。

模块化方案还有其他益处,例如均流、相位交错、供电网络 (PDN) 的引入以及输入/输出电容的优化等。

多相配置设置

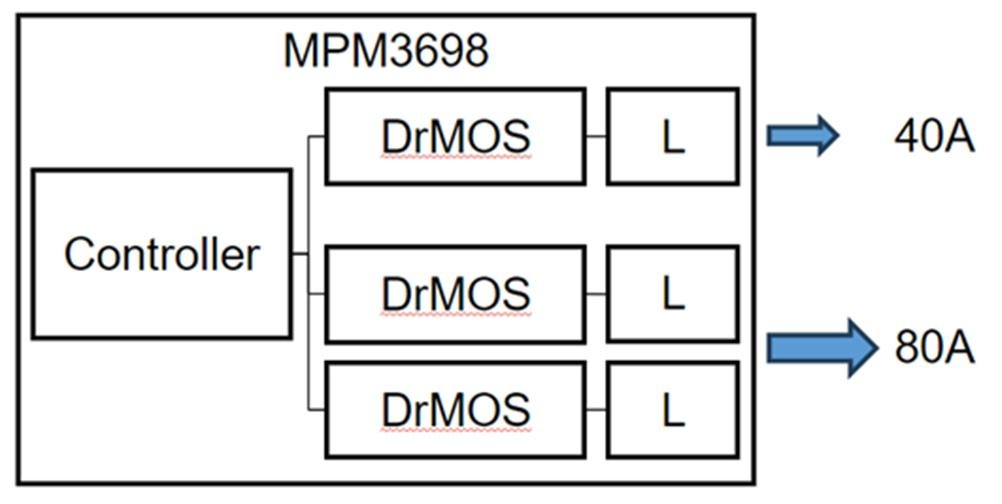

MPM3698是一款全集成电源模块,支持单路峰值120A或双路峰值80A+40A输出,并配备数字接口。该模块集成了符合VR14标准的双环路数字多相控制器,以及三组驱动MOSFET和电感。凭借MPS专有数字多相非线性控制技术,MPM3698能够以极低的输出电容实现超快瞬态响应。

MPM3698每相可提供高达40A的峰值电流和30A的连续电流。通过三相并联输出,该模块可支持最高120A峰值 IOUT 或90A连续 IOUT。

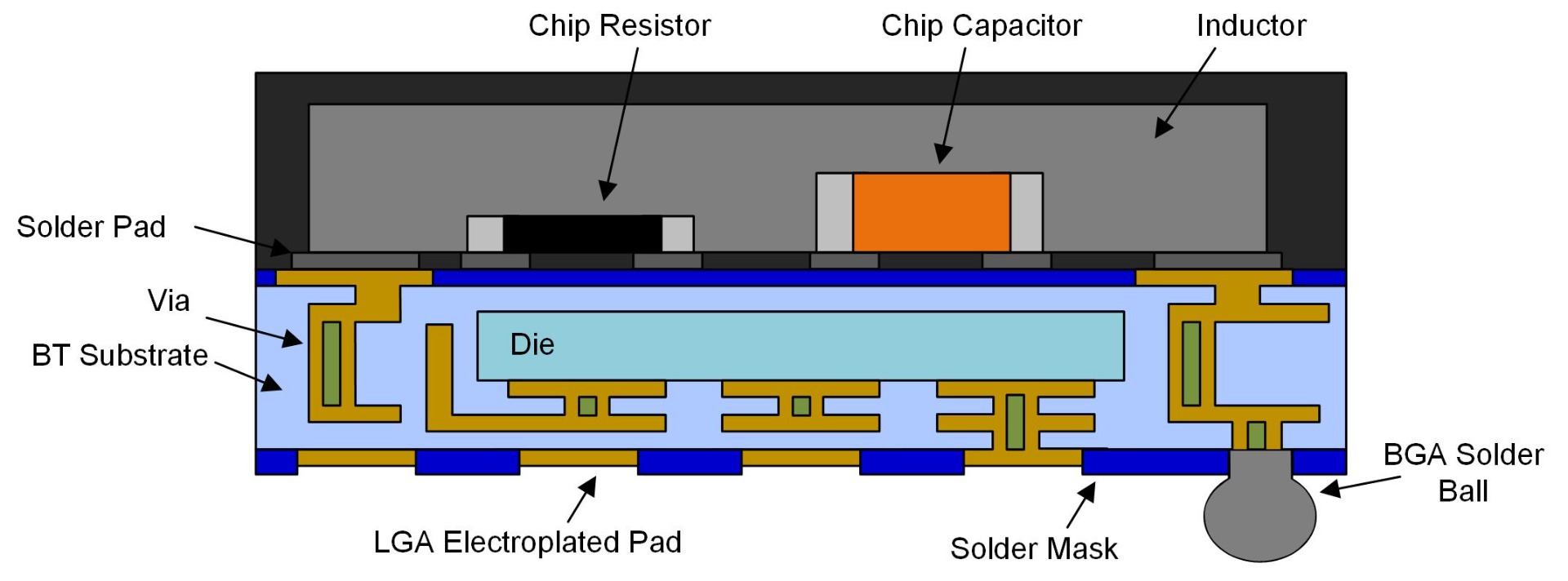

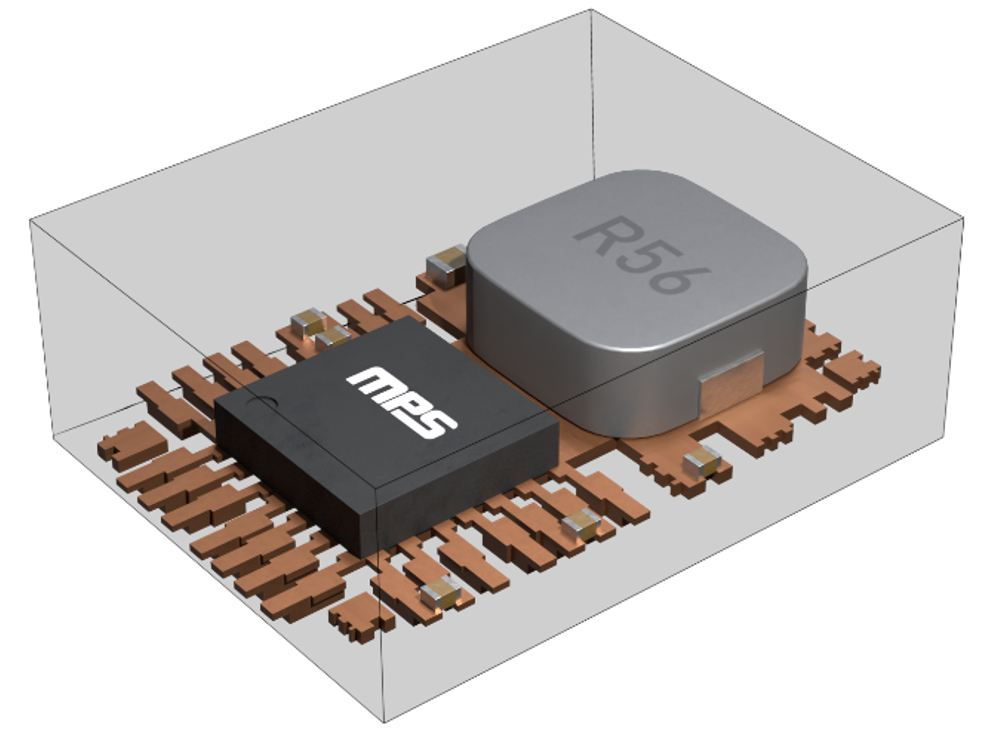

图2展示了MPM3698的内部配置。每个MPM3698模块都由三个DrMOS和一个控制器组成,总输出电流为120A 。

图2: MPM3698内部配置

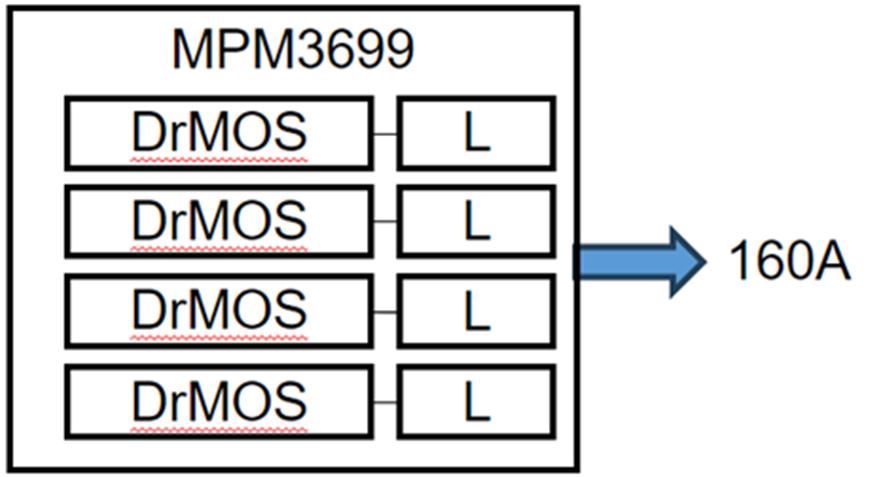

通过连接PWM控制器,配置额外模块(如MPM3699)作为外部DrMOS使用,可在原有MPM3698的基础上扩展更多相位。采用MPM3699电源模块时,系统输出电流 IOUT 可达560A甚至更高。

MPM3699内置4个DrMOS模块,可提供高达160A的 IOUT。图 3 展示了MPM3699 的内部配置。

图3: MPM3699内部配置

MPM3698负载瞬态测试

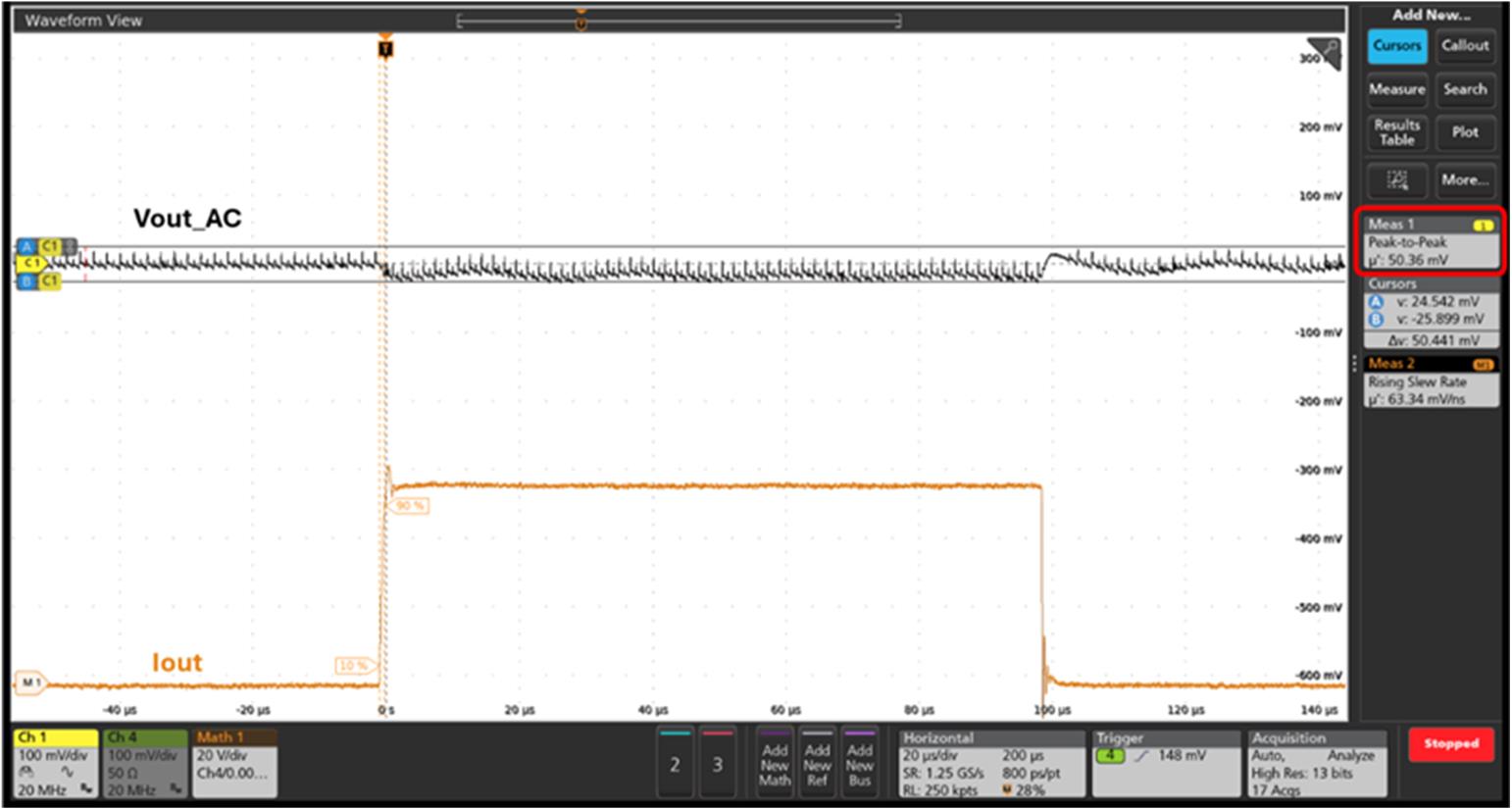

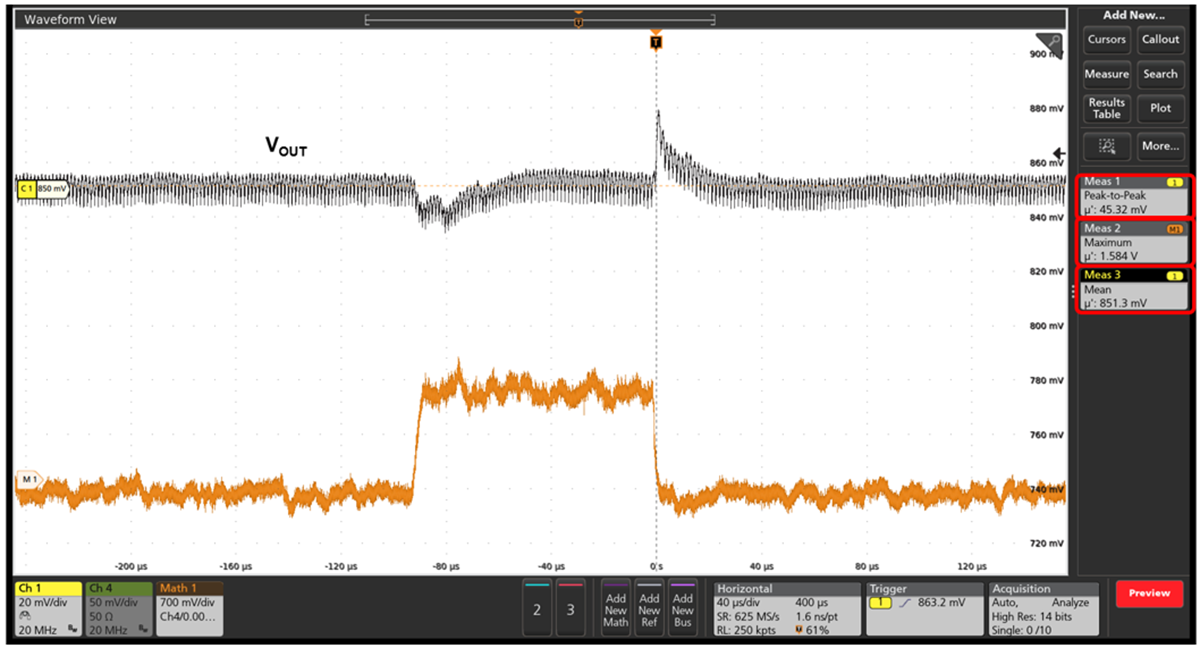

负载瞬态下的输出电压容限与稳定性是FPGA和ASIC应用最关键的参数之一。负载瞬态测试配置采用47颗47µF的MLCC(多层陶瓷电容),总容值达2.2mF;同时搭配4颗330µF的POSCAP(导电高分子电容),总容值为1.32mF。

负载瞬态测试条件设定为:输入电压 VIN12V,输出电压0.85V,最大输出电流60A(由两相均流承载,电流变化范围0A-60A)。测试结果表明,该系统具有卓越的瞬态响应性能,其输出电压 (VOUT/AC) 始终保持在±3%(即±30mV)的容差范围内(见图4),该指标完全满足FPGA核心电压轨 VCORE 的标准要求。

图4:瞬态响应测试(1个模块,2相,负载瞬态范围0A至60A,峰峰值电压在±30mV容差范围内)

根据负载瞬态测试结果,MPM3698完全满足FPGA核心电压轨对瞬态响应的严苛要求:当输出电压 VOUT为0.85V时,其峰峰值纹波为50.36mV,符合I/O电压±3%(即±30mV)的容差标准。

结语

鉴于FPGA和ASIC对供电系统的严苛要求,多相降压变换器已成为高性能设备供电的关键解决方案。采用多相架构既能实现大电流输出,又可提供低电压。多相电源具备快速瞬态响应特性,能将电压波动严格控制在±3%容差范围内,这一指标对现代FPGA/ASIC的核心及辅助电源轨极为重要。

MPM3698采用MPS专有数字多相非线性控制技术,可实现超快负载瞬态响应。该模块还具有设计简洁、布局灵活、体积紧凑等优势。通过多相均流技术,MPM3698/MPM3699等器件能显著提升效率、降低热应力,并减少输入输出电容需求。敬请了解更多MPS电源模块产品,以实现出色的相位交错等优异性能。

_______________________

您感兴趣吗?点击订阅,我们将每月为您发送最具价值的资讯!

技术论坛

Latest activity 3 years ago

Latest activity 3 years ago

2 回复

2 回复

Latest activity 3 years ago

Latest activity 3 years ago

2 回复

2 回复

Latest activity 3 years ago

Latest activity 3 years ago

6 回复

6 回复

直接登录

创建新帐号